P1

实验内容¶

实验一¶

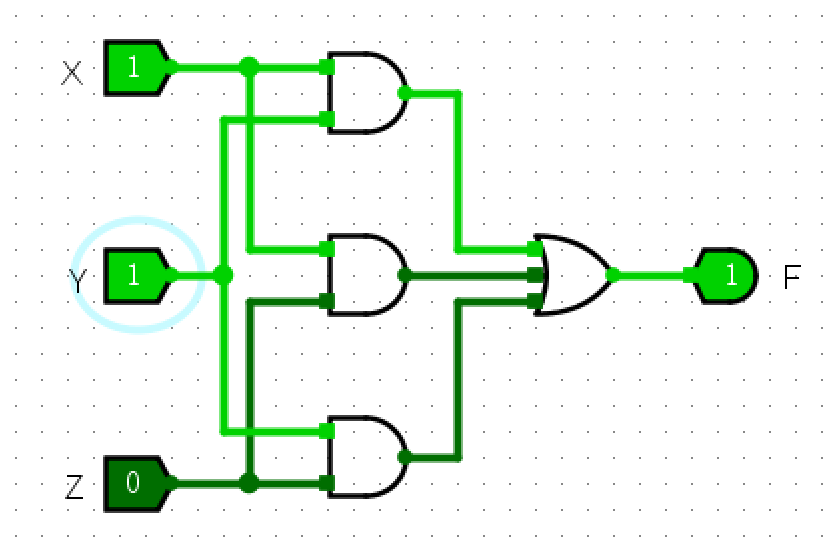

- 利用基本逻辑门设计一个 3 输入多数表决器。

整体方案设计¶

输入输出引脚¶

- XYZ:三个输入项,链接三个“表决”数据

- F:输出项,得到表决数是否大于等于2,即占多数

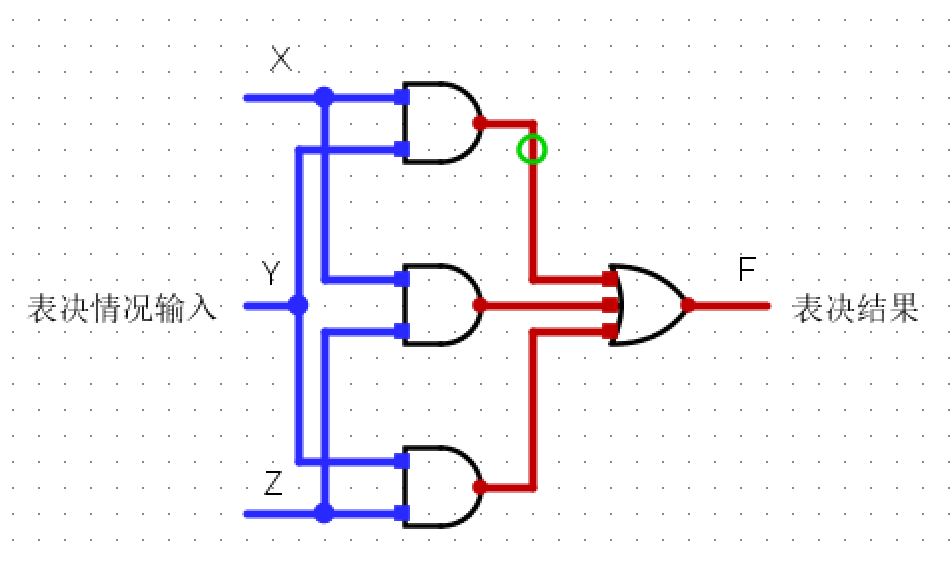

原理图和电路图¶

- 原理图

-

-

电路图

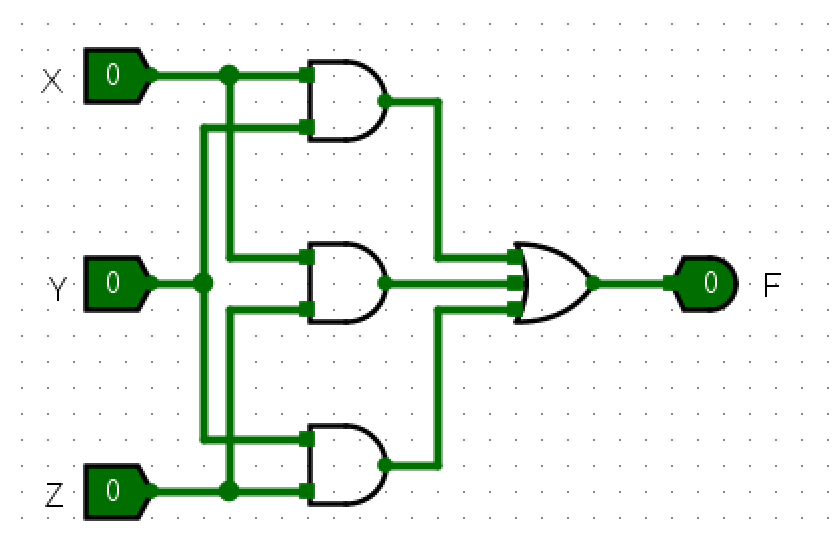

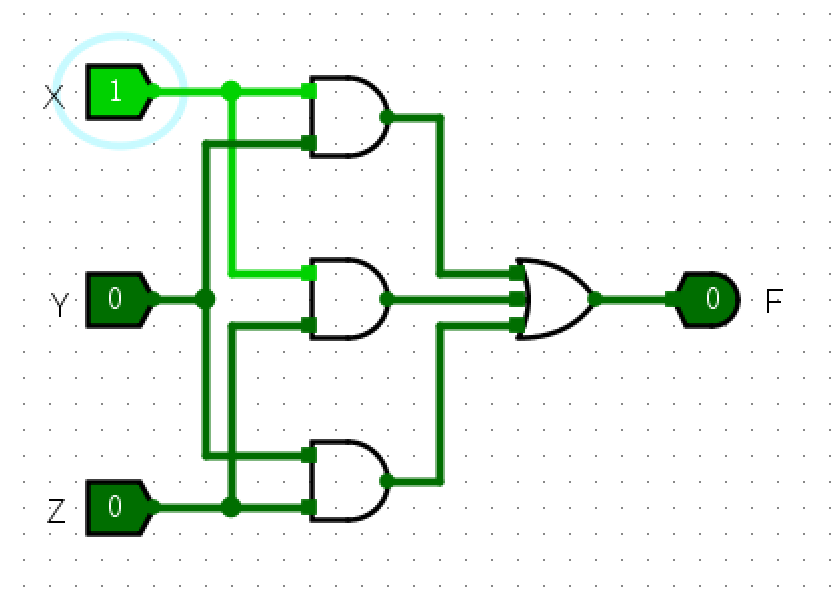

仿真测试¶

代表性输入输出¶

- \(X=1 \ Y=0 \ Z=0\)

- \(X=1 \ Y=1 \ Z=0\)

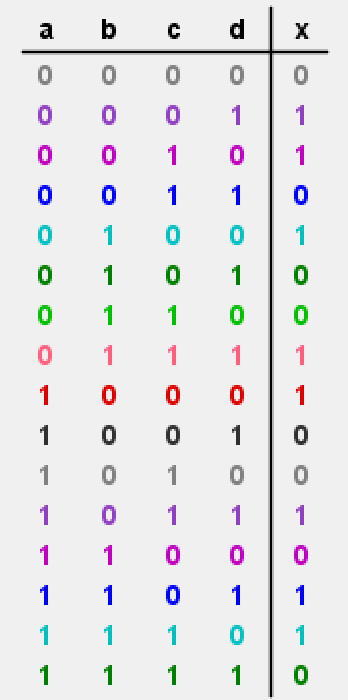

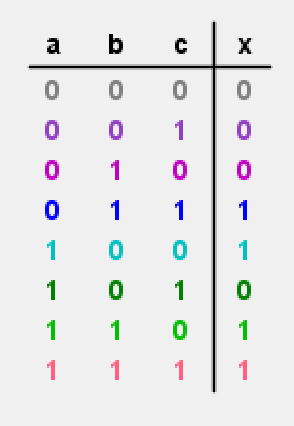

真值表¶

错误现象及分析¶

- 在完成实验的过程中,没有遇到任何错误。

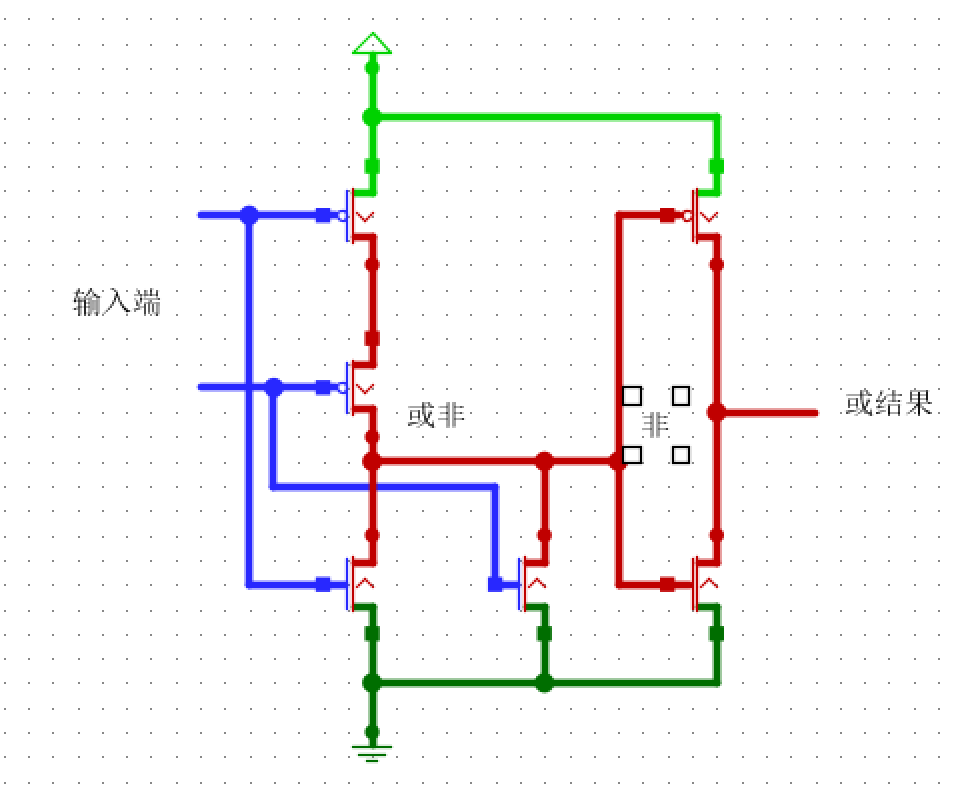

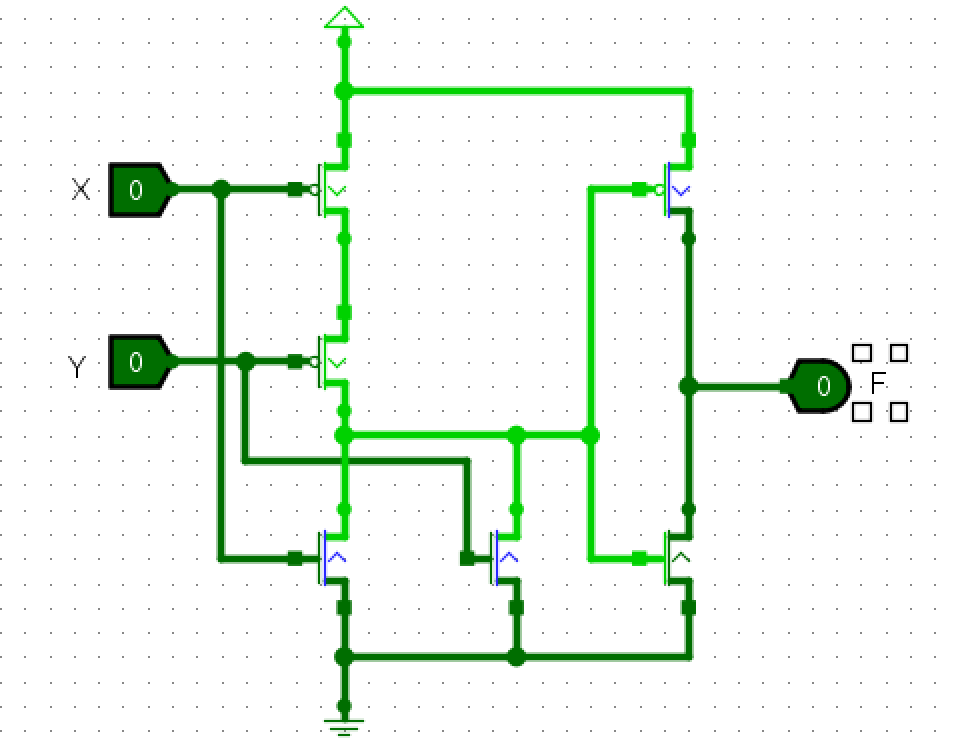

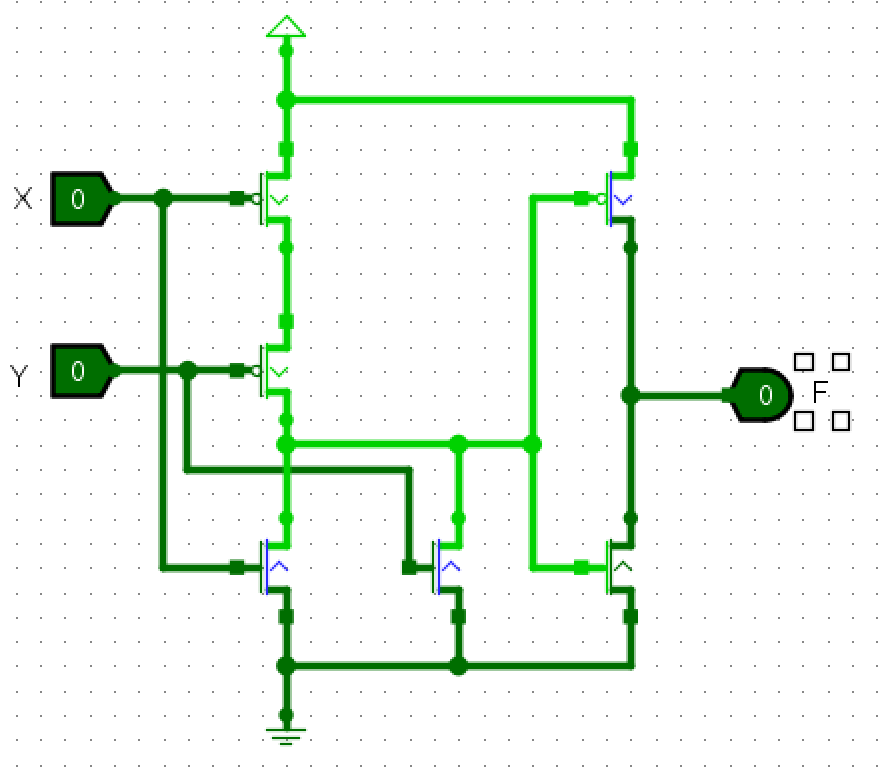

实验二 CMOS 晶体管构建两输入或门¶

- 利用 CMOS 晶体管构建两输入或门,并验证其功能。

整体方案设计¶

输入输出引脚¶

- XY:两个输入

- F:或结果输出

原理图和电路图¶

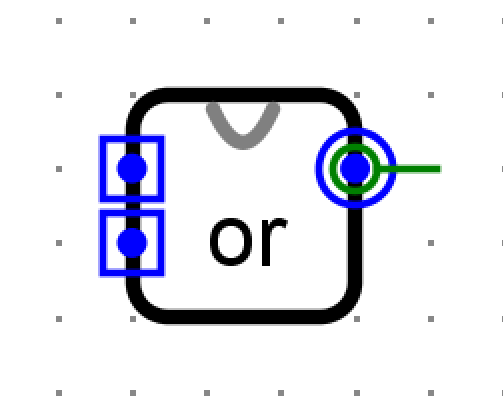

- 原理图

- 电路图

仿真测试¶

代表性输入输出¶

- \(X=0 \ Y=0\)

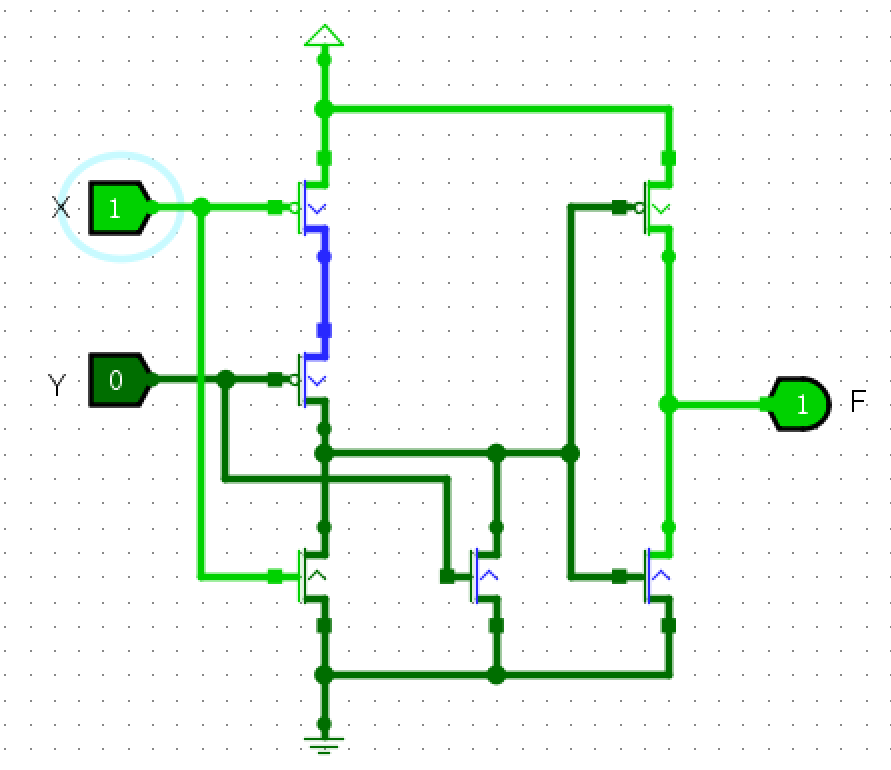

- \(X=1 \ Y=0\)

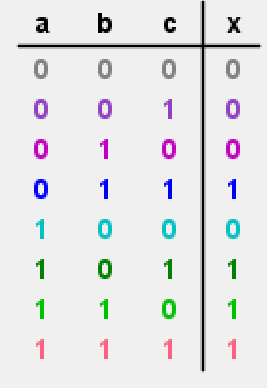

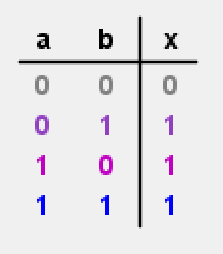

真值表¶

错误现象及分析¶

- 在完成实验的过程中,没有遇到任何错误。

实验三 2-1MUX-hazard¶

- 利用基本逻辑门和 CMOS 晶体管实现多路选择器。

整体方案设计¶

输入输出引脚¶

- D0,D1:两个输入端

- S:控制端,用于从D1,D2中选择作为结果

原理图和电路图¶

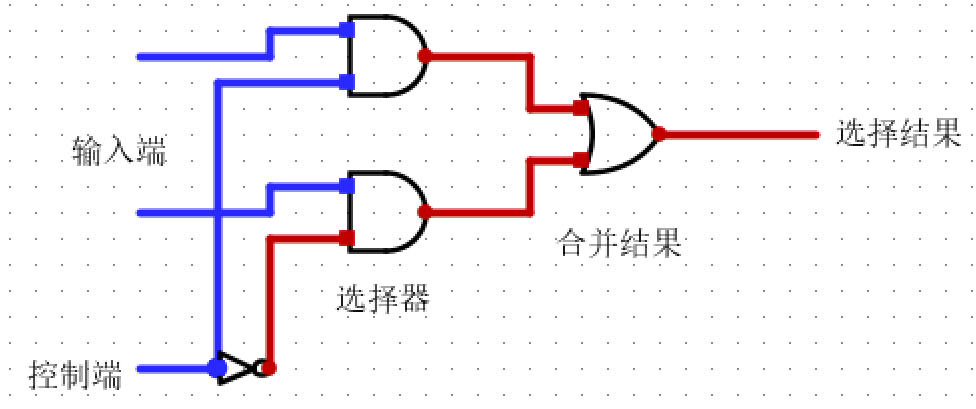

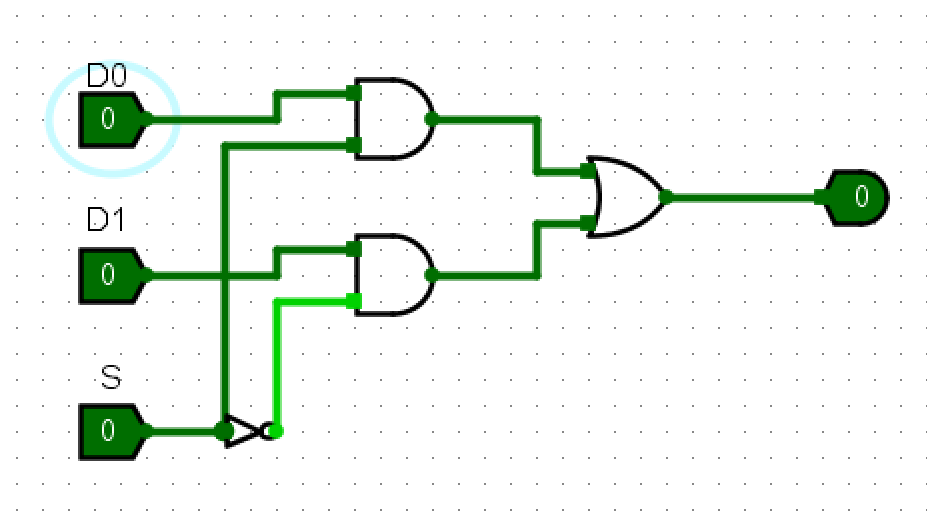

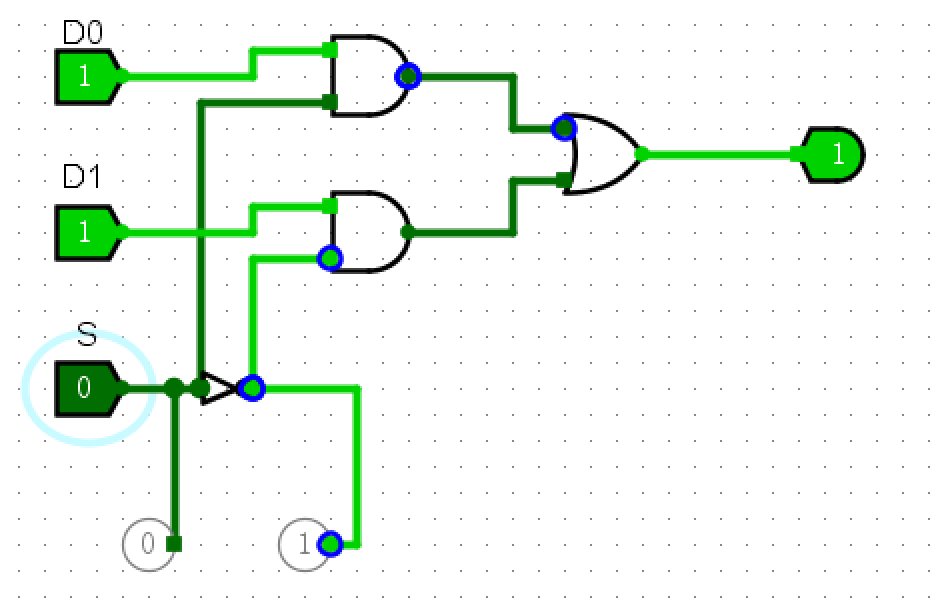

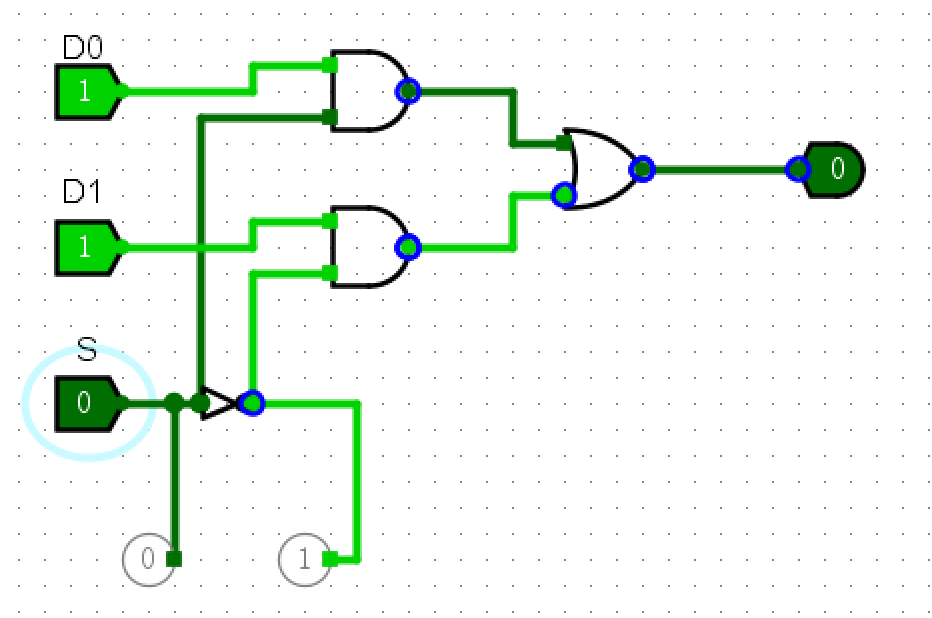

- 原理图

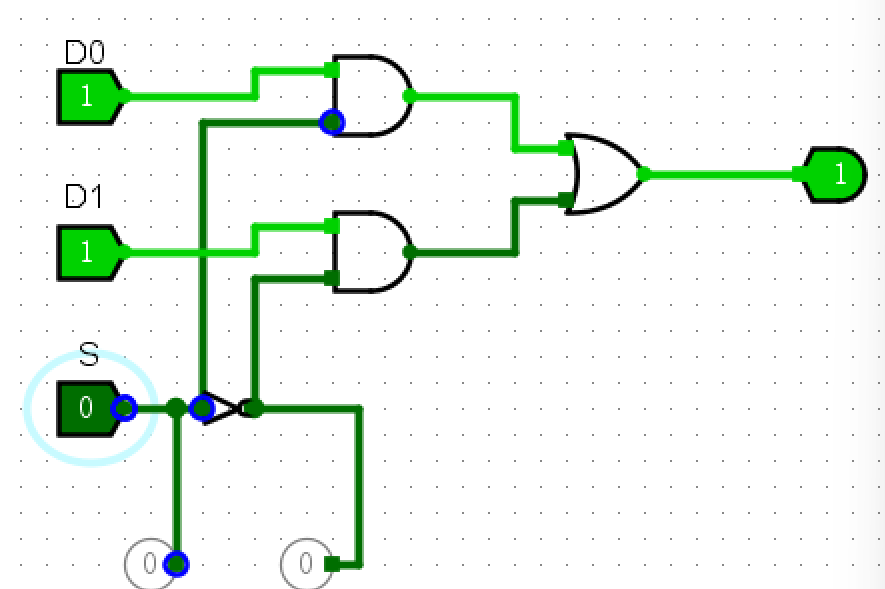

- 电路图

仿真测试¶

冒险检测¶

- S从1变化为0时可能产生临时的错误结果

- 出现异常

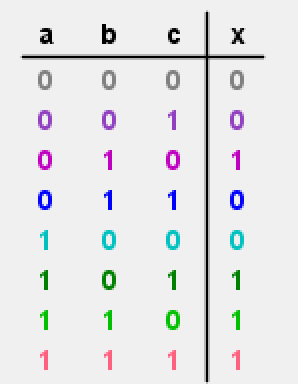

真值表¶

错误现象及分析¶

- 在完成实验的过程中,没有遇到任何错误。

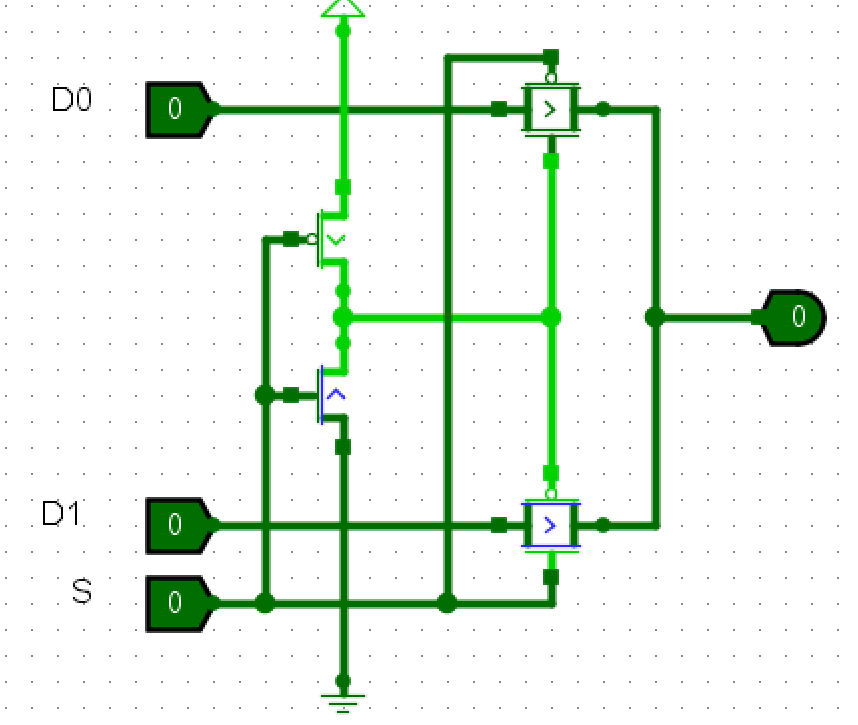

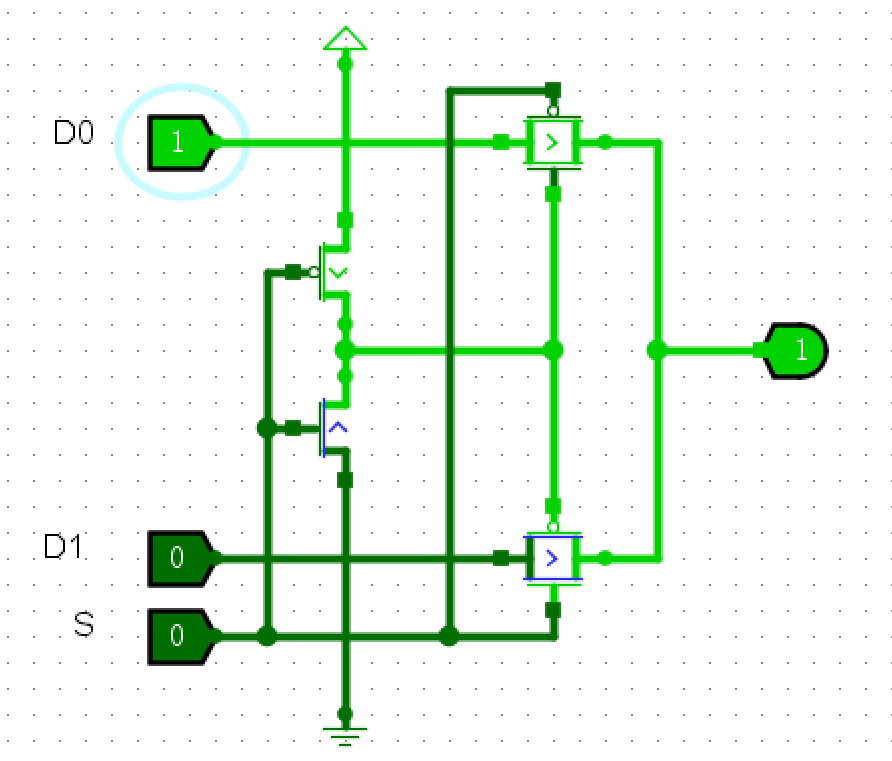

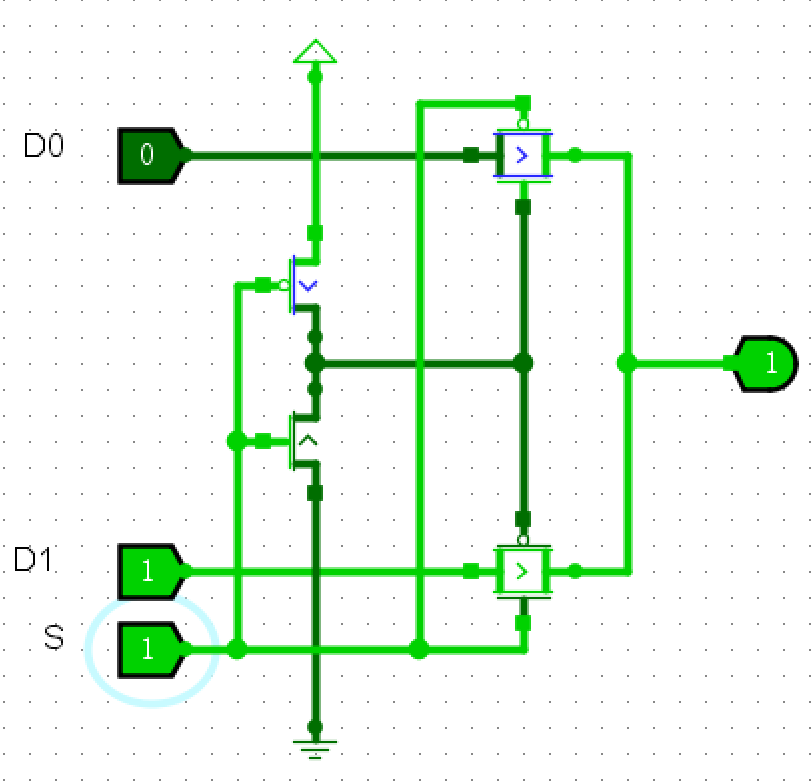

实验四 2-1MUX-hazard-2¶

- 使用传输门实现选择器

整体方案设计¶

输入输出引脚¶

- D0,D1:两个输入端

- S:控制端,用于从D1,D2中选择作为结果

原理图和电路图¶

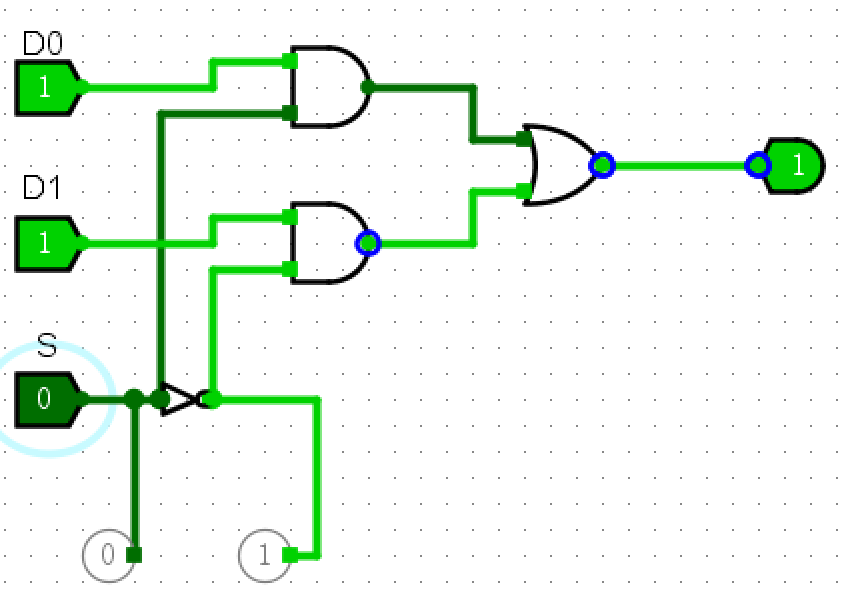

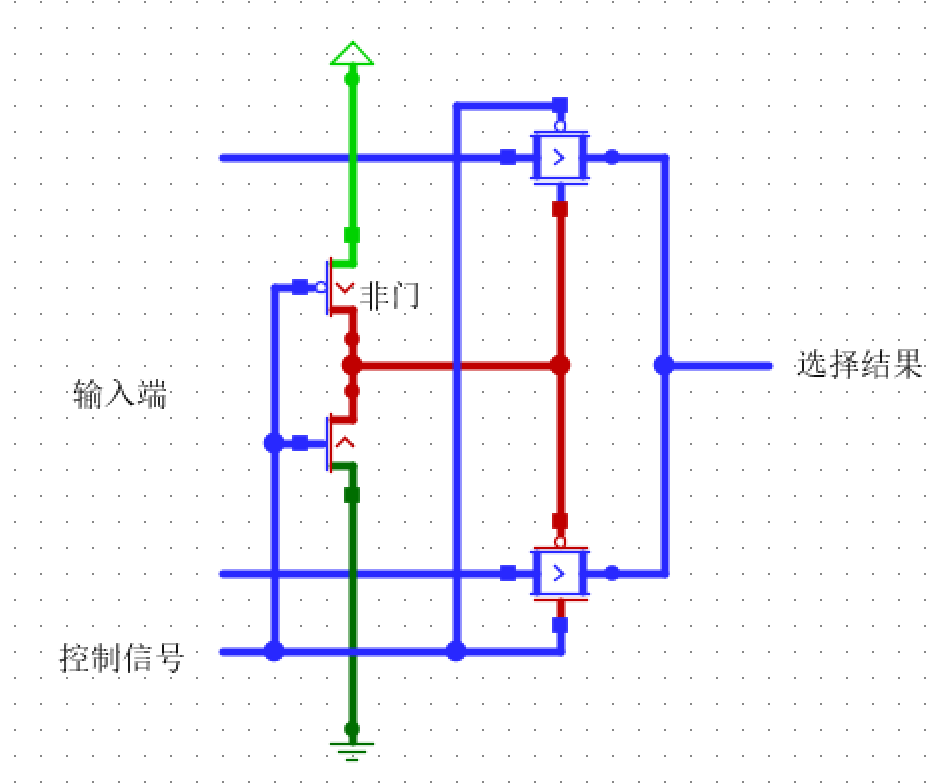

- 原理图

- 电路图

仿真测试¶

代表性输入输出¶

- \(D0=1 \ D2=0 \ S=0\)

- \(D0=0 \ D2=1 \ S=1\)

真值表¶

错误现象及分析¶

- 在完成实验的过程中,没有遇到任何错误。

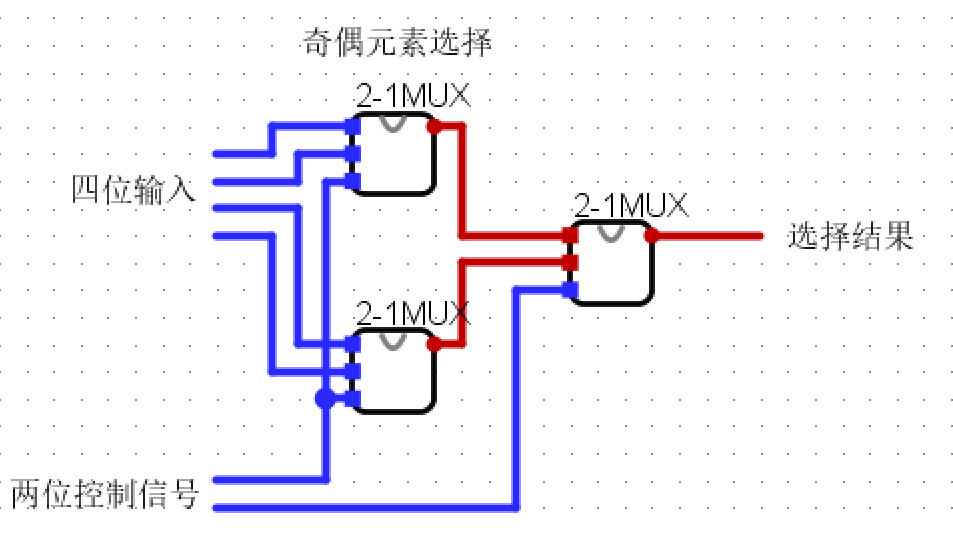

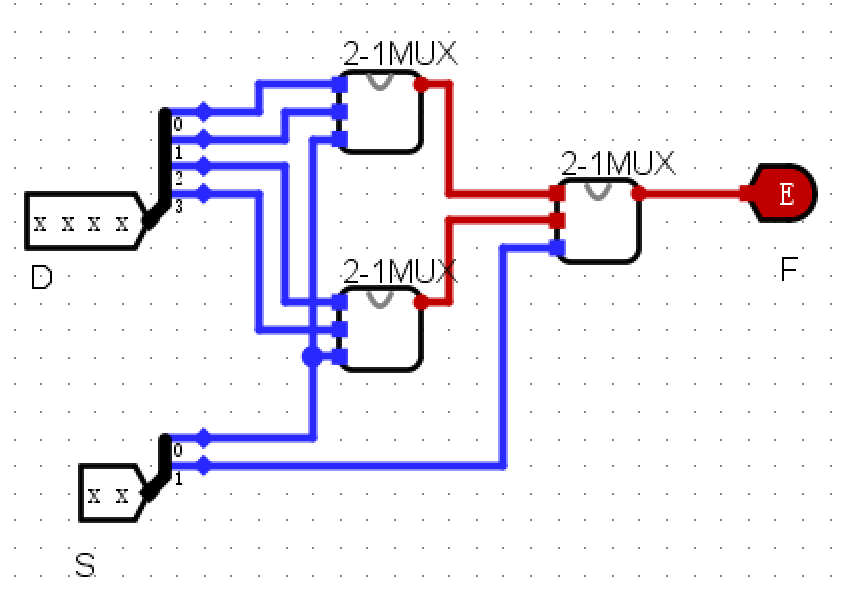

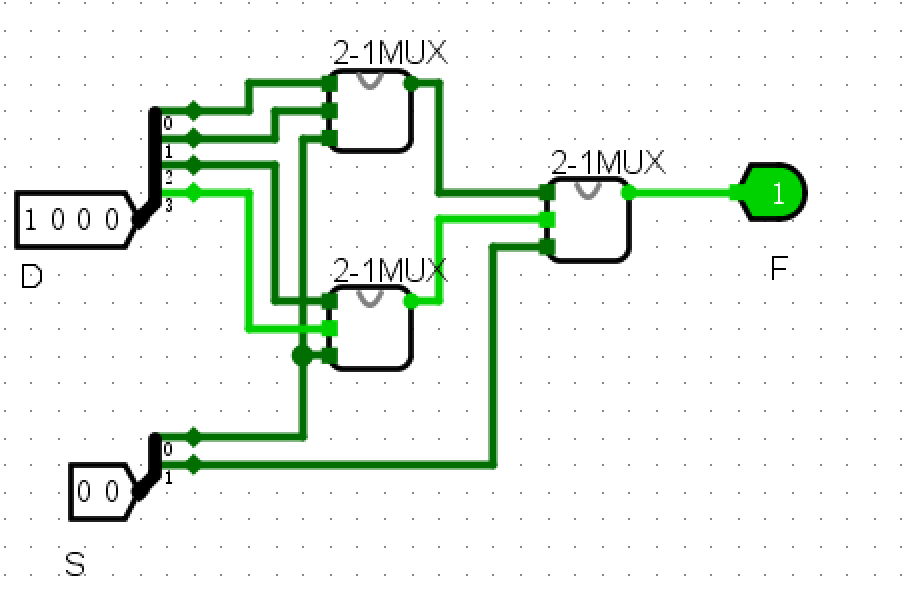

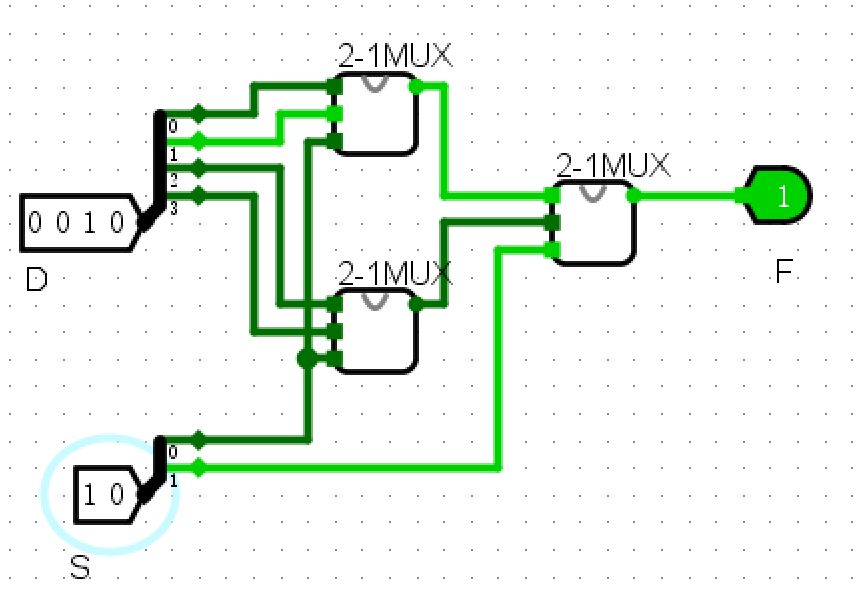

实验五 4-1MUX-hazard¶

整体方案设计¶

输入输出引脚¶

- D(D0~D3):四位输入

- S(S0~S1):两位控制信号,用于选择输入作为结果

原理图和电路图¶

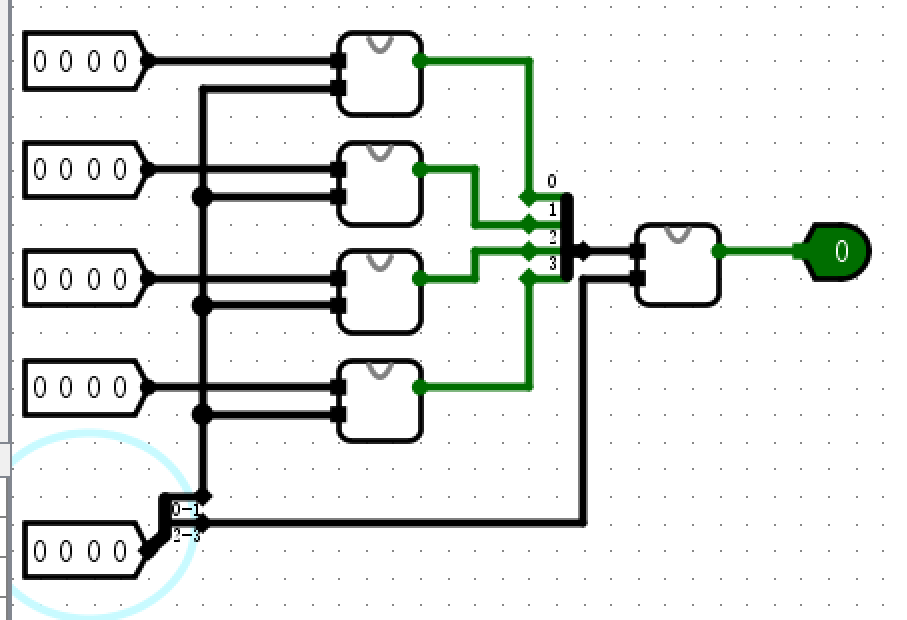

- 原理图

- 电路图

仿真测试¶

代表性输入输出¶

- \(D=0001 \ S=00\)

- \(D=0100 \ S=01\)

真值表¶

- S为00时选择D3;s为01时选择D1;s为10时选择D2;s为11时选择D0;

- 由于输入过多,真值表不再赘述。

错误现象及分析¶

- 在完成实验的过程中,没有遇到任何错误。

思考题¶

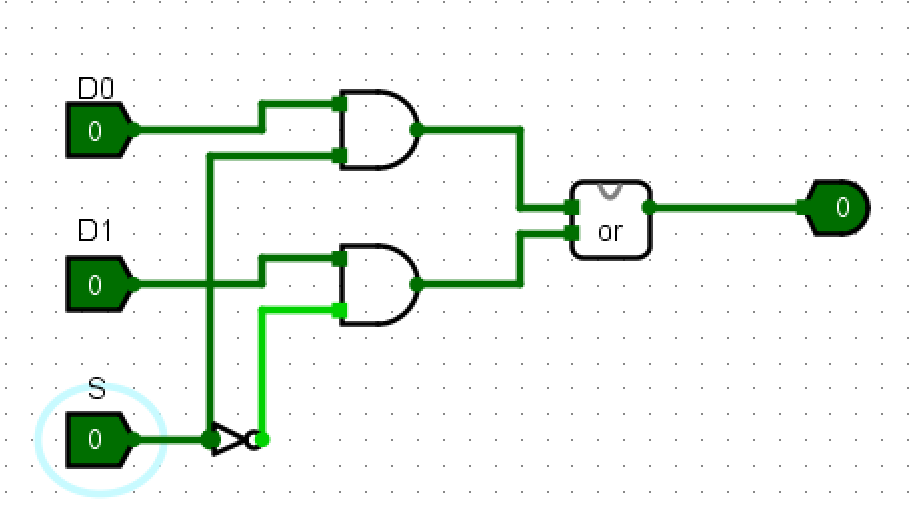

将实验中设计的或门作为子电路应用到 2-1MUX-hazard 电路中¶

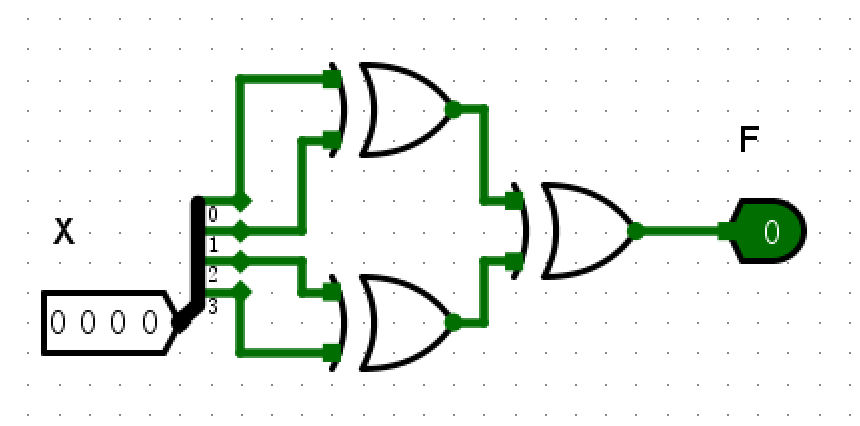

- 电路图

- 对实验二中的或门进行打包

修改现有电路设计实现 4 位 4 选 1 多路选择器¶

- 电路图

设计并实现 4 位二进制数的奇偶校验位生成电路¶

- 分析:通过对4位每一位进行异或操作,即可得到奇偶校验码

- 引脚

- X(X0~X3):4位输入

- F:奇偶校验码结果

- 电路图

- 真值表