****## 时序逻辑电路

- 组合逻辑电路的输出结果仅取决于当前的输入信号

- 时序逻辑电路的输出结果不仅取决于当前时刻的输入值,还取决于电路过去时刻的行为

- 电路中有存储元件,用于存储逻辑信号的值,表示电路过去时刻的行为(当前状态、现态、旧状态)

- 即下一状态受到当前状态和当前输入的影响

有限状态机¶

- 有限状态机FSM是刻画状态以及状态转换的理论工具

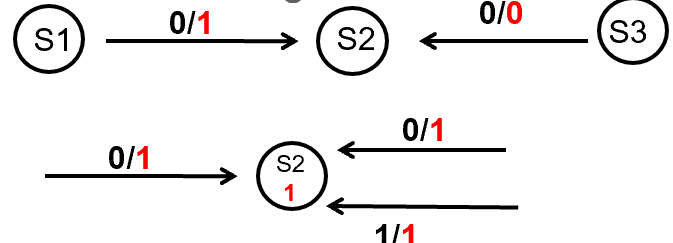

- 状态图

- 用包含状态符号的圆圈表示状态

-

用有向边表示状态转换方向,并在边上标注引起状态变换的输入信号值和相应输出

- 若输出只与当前状态有关,则把输出标注在状态圆圈中

-

-

-

用数字电路实现

- 把状态机的输入、输出以及内部状态都转换成二进制表示,作为状态的二进制编码

- 使用状态记忆电路

-

设计状态记忆电路的激励函数(根据当前输入把旧状态改为新状态的函数)和输出函数(根据旧状态和当前输入来改变电路输出结果的函数),并完成定时分析。

-

能实现有限状态机的数字逻辑电路就是时序逻辑电路

- 时序逻辑电路中输出可以也必须回到输入端

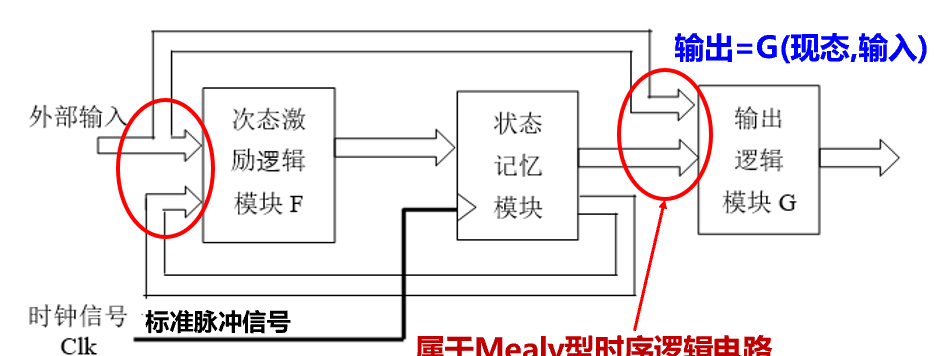

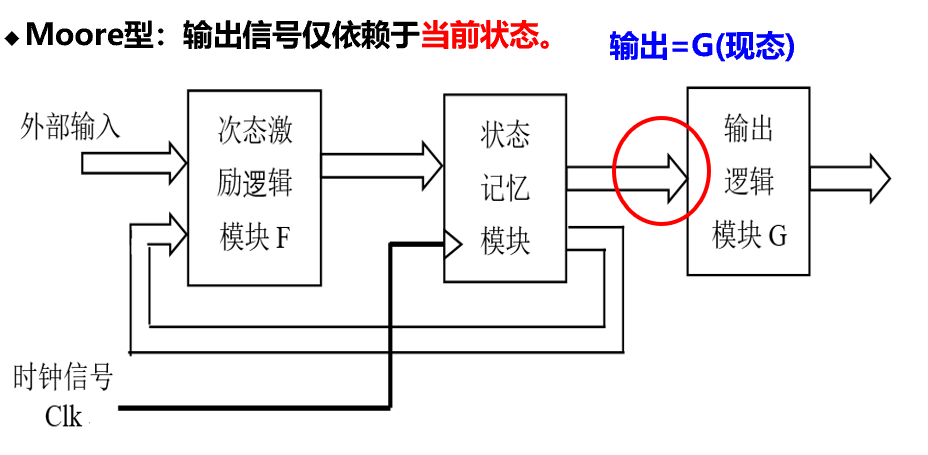

基本结构¶

- 状态记忆模块:存储单元(由多个状态记忆单元构成)

- 次态激励逻辑模块F :激励函数(现态和外部输入的逻辑函数)

- 输出逻辑模块 G :输出函数(现态和[外部输入]的逻辑函数)

- Mealy型:输出依赖于当前状态和当前输入信号

- Moore型:输出仅依赖于当前状态,和当前输入信号无关

时钟脉冲¶

- 根据状态转换方式分类

- 同步时序逻辑电路:在统一的时钟信号控制下进行状态转换

-

异步时序逻辑电路:没有统一的时钟信号来控制状态的改变

-

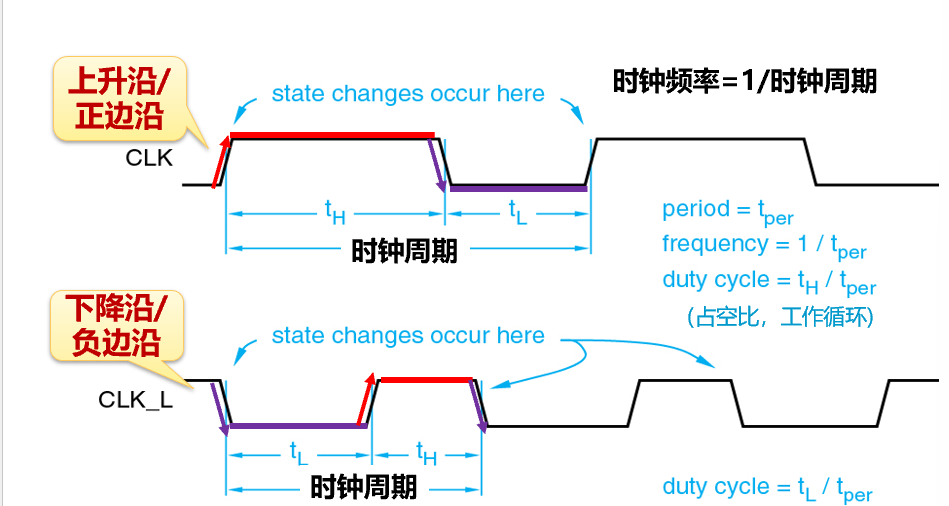

时钟脉冲

- 按一定电压幅度、按固定时间间隔、连续发出的脉冲信号

- 时钟脉冲之间的时间间隔称为时钟周期。单位是秒。

- 通常将1秒内所产生的脉冲个数称为时钟频率。

-

单位是Hz 计算机中的系统时钟就是一个典型的、频率精确和稳定的脉冲信号发生器。

-

时钟脉冲触发状态转换

- 电平触发/边沿触发

- 边沿触发:上升沿触发、下降沿触发

锁存器和触发器¶

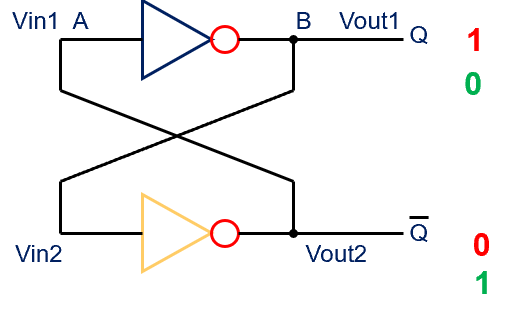

双稳态存储元件¶

-

虽然下次状态和当前状态不直接相关,但是仍然算是一种特殊的时序逻辑电路

-

用于存储1位二进制数据,有两个互补的输出状态

- 状态1:置位,即1

- 状态0:复位,即0

- 简单实现

-

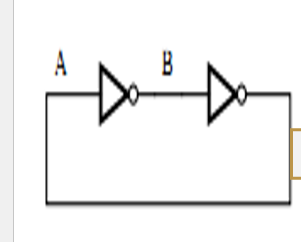

串联两个反相器,会保持稳定

-

交叉耦合:

- Q为高点平时为置位状态;Q为低电平时为复位状态

-

用两个反相器串联构建的双稳态元件无法改变电路状态

-

用1个或多个输入信号能驱动双稳态元件进入稳定状态,这些输入信号称为激励信号或激励输入。通常根据不同的激励输入信号来命名存储元件,如SR、JK、D、T 等不同的激励输入信号

锁存器¶

- 用激励信号的电平触发

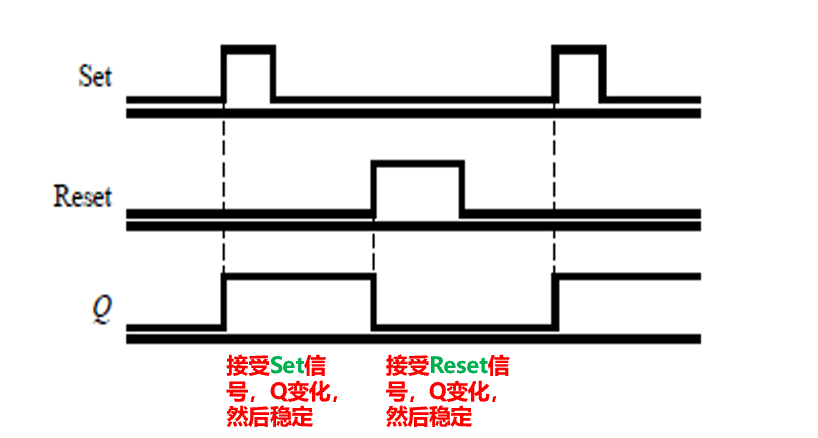

- 置位复位锁存器:具有置位和复位激励信号。置位激励信号Set有效时,强制存储元件的输出Q为1;复位激励信号Reset有效时,强制存储元件的输出Q为0

-

-

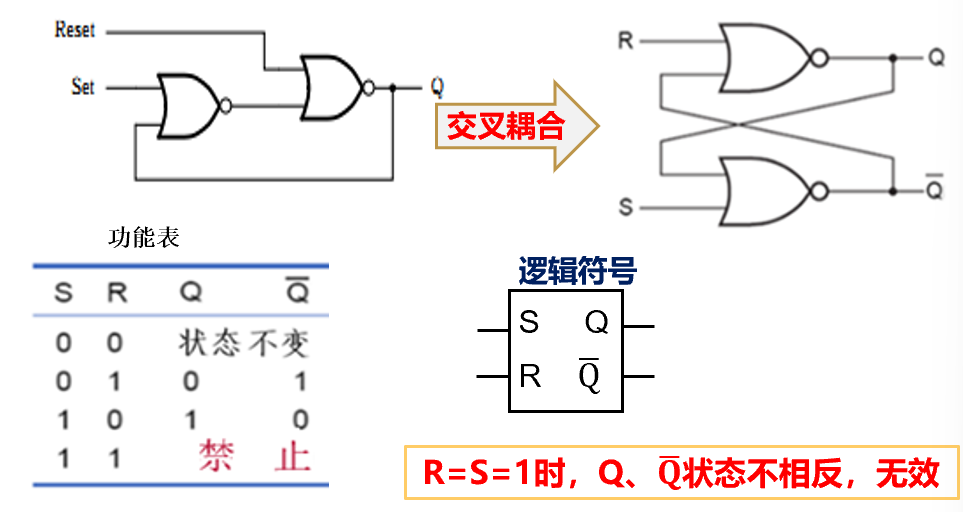

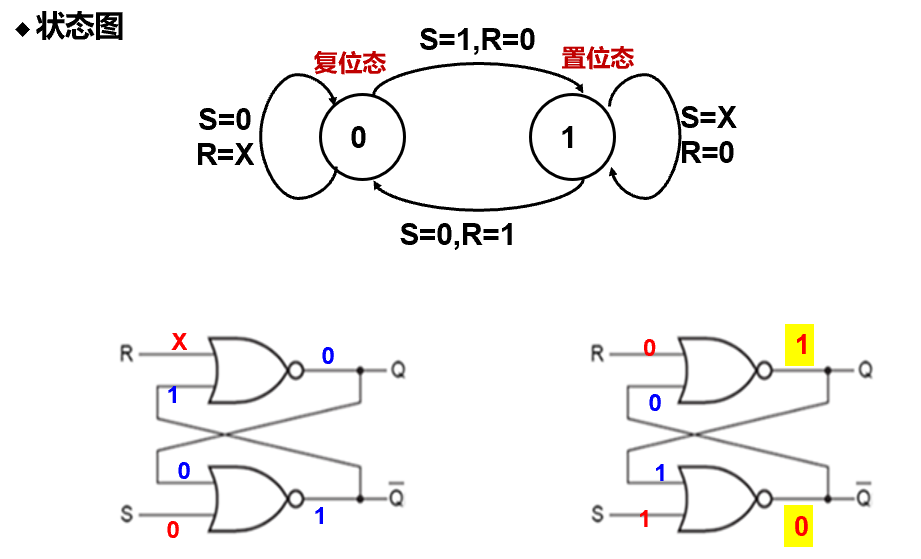

SR 锁存器:一对交叉耦合的或非门构成双稳态电路

- SR锁存器只有状态没有输出,常用来设置标志位

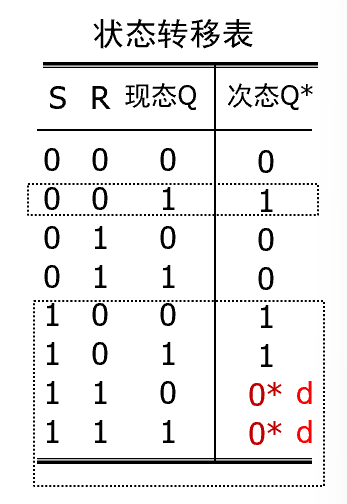

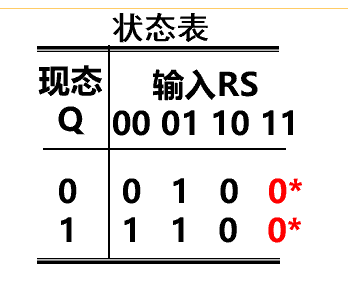

- 时序逻辑电路的状态表

- 从输入驱动信号有效开始,到输出达到稳定为止有一定的延迟,这个延迟称为触发延迟或锁存延迟。

- 状态转移表

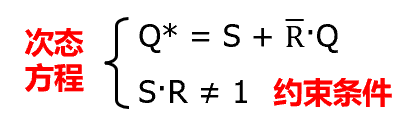

- 次态(特征)方程

-

状态图、状态表、状态转移表、特征方程是时序逻辑电路的不同描述

-

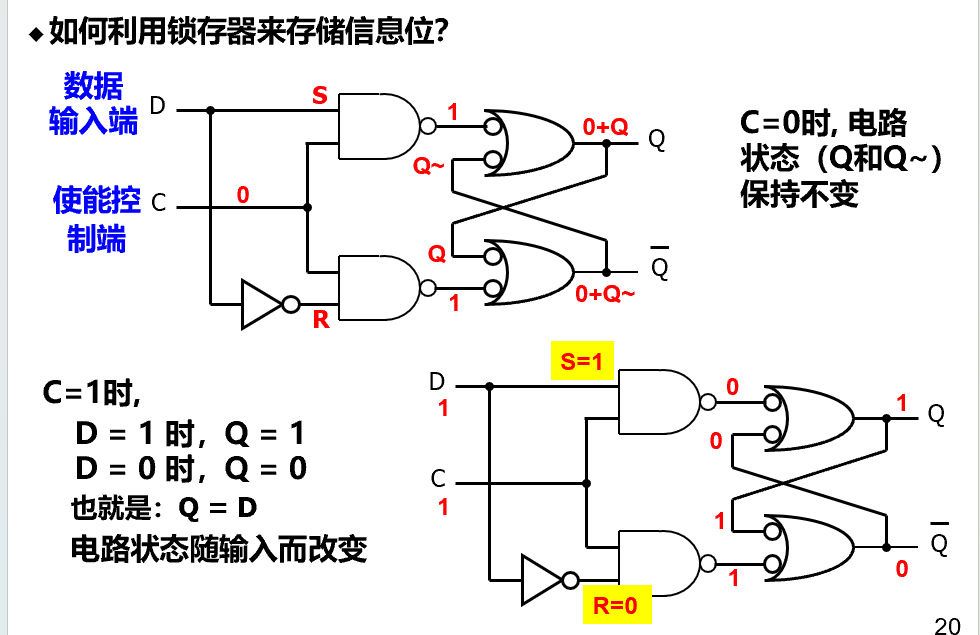

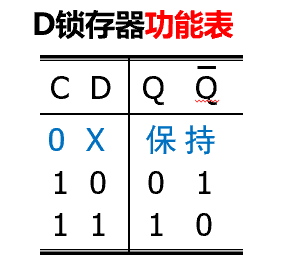

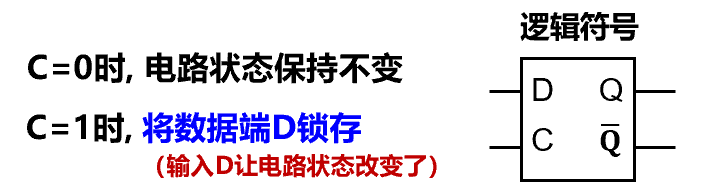

D锁存器

- 只有一个数据输入端D,称为D锁存器,也称为透明锁存器

- 即\(C=0\)时,相当于SR锁存器的\(S=0,R=0\),固信号不发生变化

- \(C=1\)时,相当于\(SR\)中一项为1

- D锁存器就是在SR上套了一个控制层

触发器¶

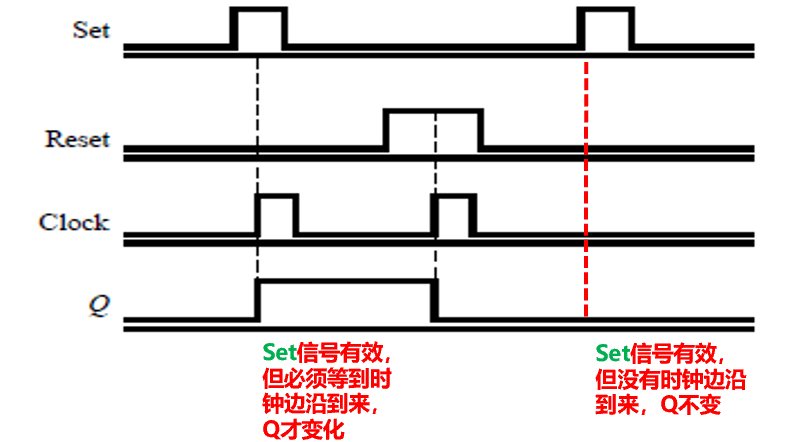

- 用时钟信号的边沿触发(也就是激励信号生效是有延迟的,需要等到下一个时钟信号到来)

-

-

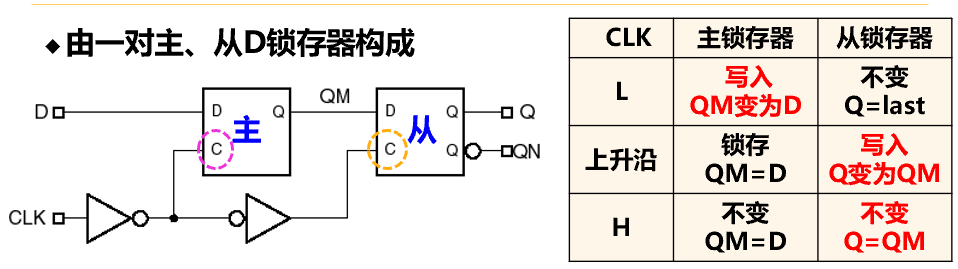

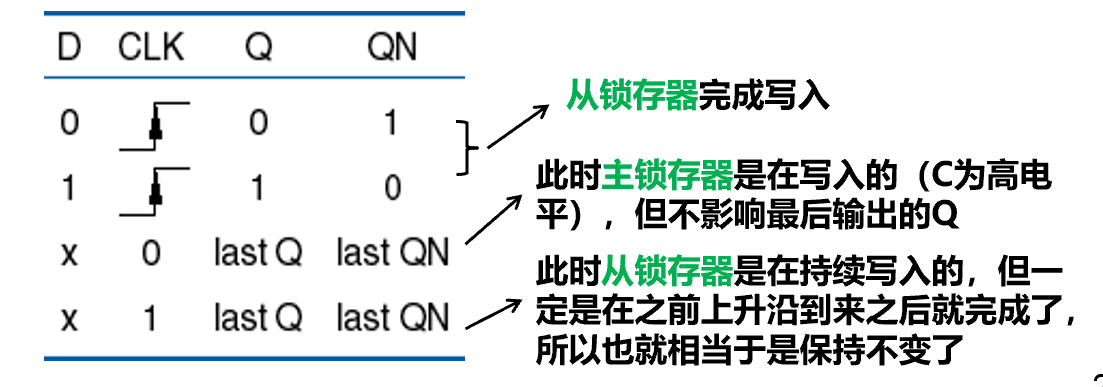

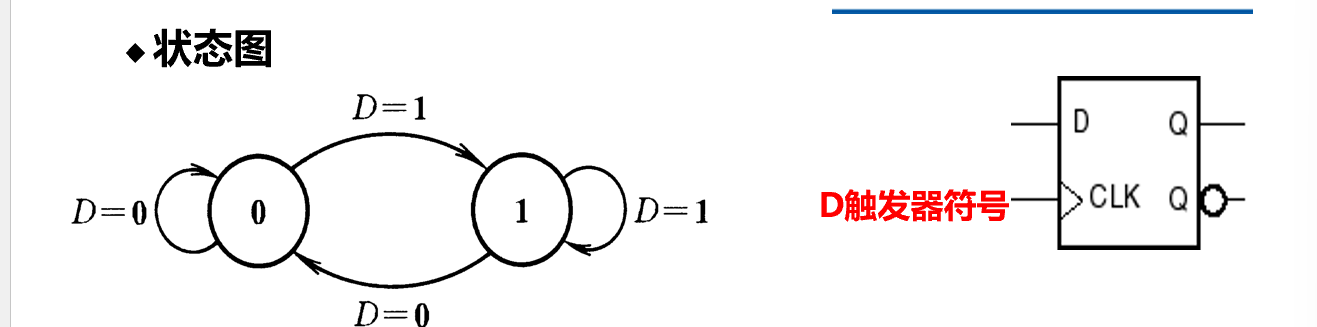

D触发器

-

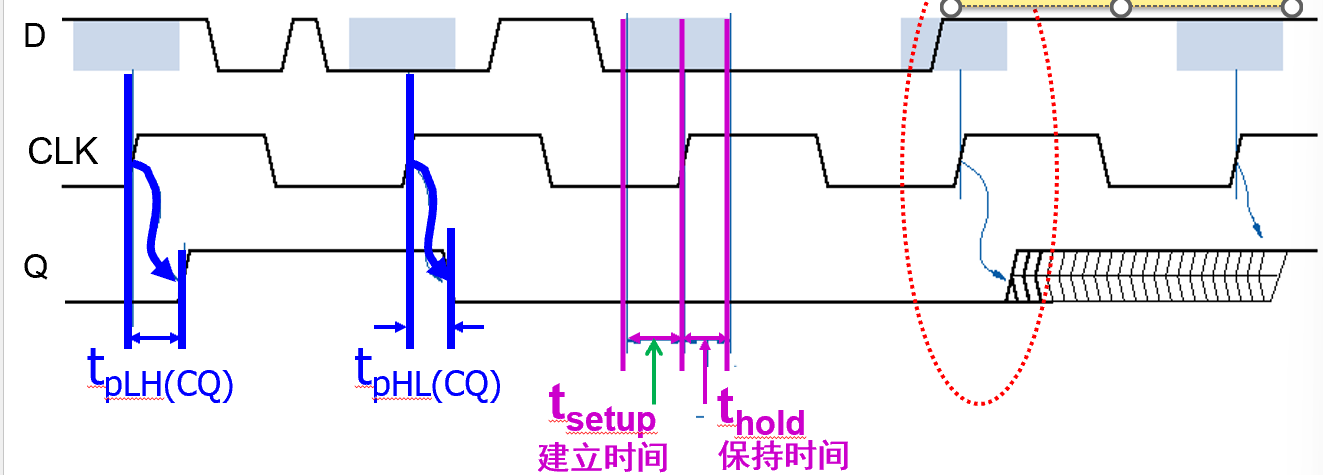

时延

- 从时钟触发边沿到来,到输出端 Q 改变为 Q 的时间称为锁存延迟,分为 \(t_{pLH}\) 和 \(t_{pHL}\)

- 建立时间\(t_{setup}\):输入信号D在时钟边沿到达前需稳定的时间

- 保持时间\(t_{hold}\):输入信号D在时钟边沿到达后需继续稳定的是啊金

- 窗口期内D输入的改变导致输出不可预测

- \(t_{hold}\) 还没结束,触发器输出就变了,这样是不行的

-

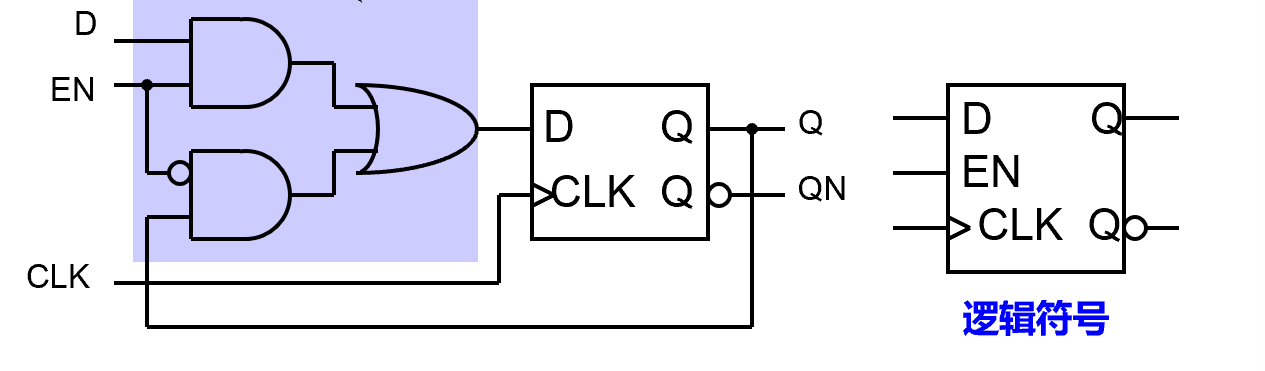

带使能端的D触发器

- 通过使能端EN信号来控制是否在时钟信号的触发边沿进行数据的存储

- 使用2选1多路选择器

- EN有效=1:选择外部D输入

- EN无效=0:保持触发器当前的输出

-

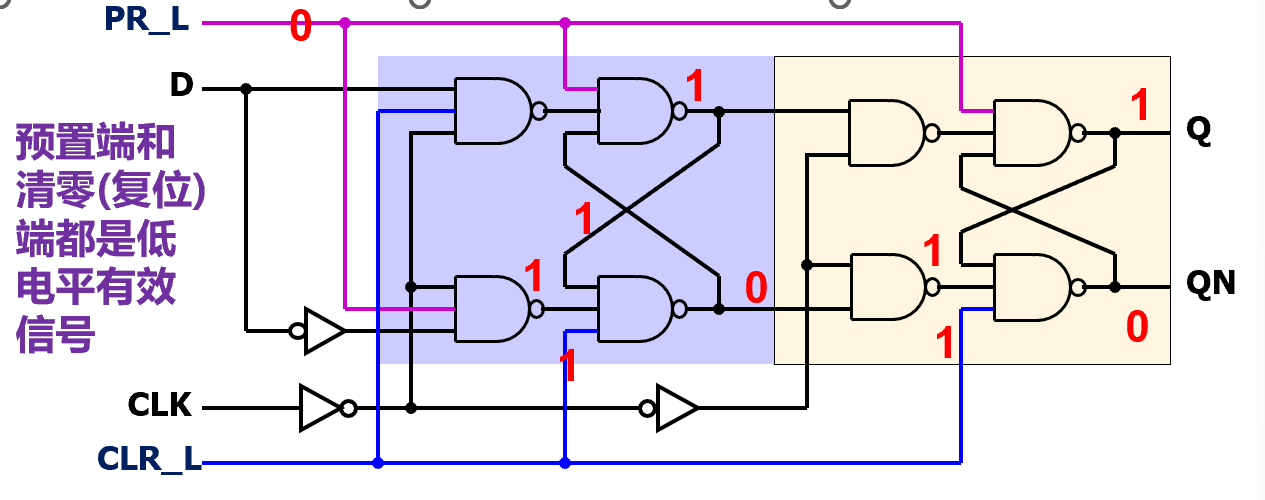

具有预置和清零的D触发器

- 预置端PR:将Q置1

- 清零端:将Q清0

-

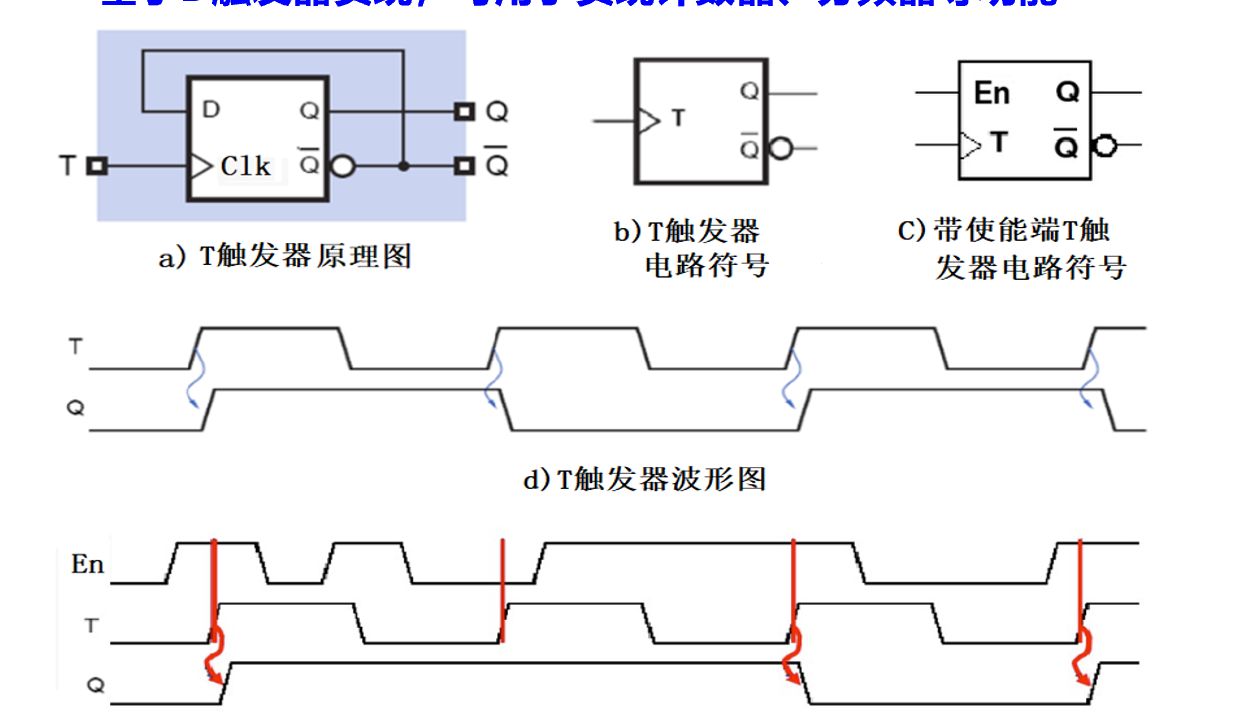

T触发器

- 在每个时钟脉冲T的触发边沿都会改变状态

- 基于D触发器实现,可以用于计数器分频器等

同步时序电路设计¶

难点¶

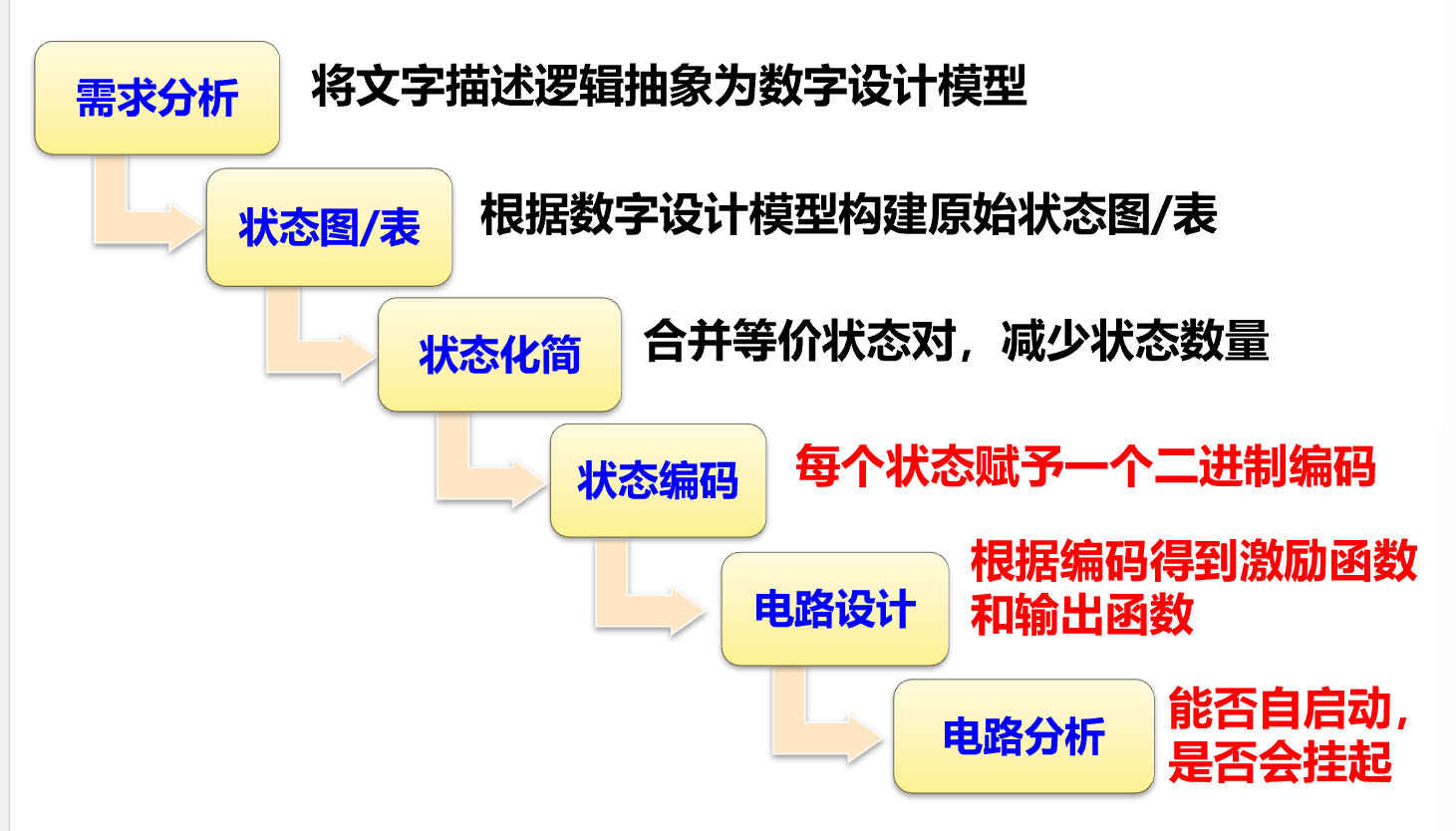

基本步骤¶

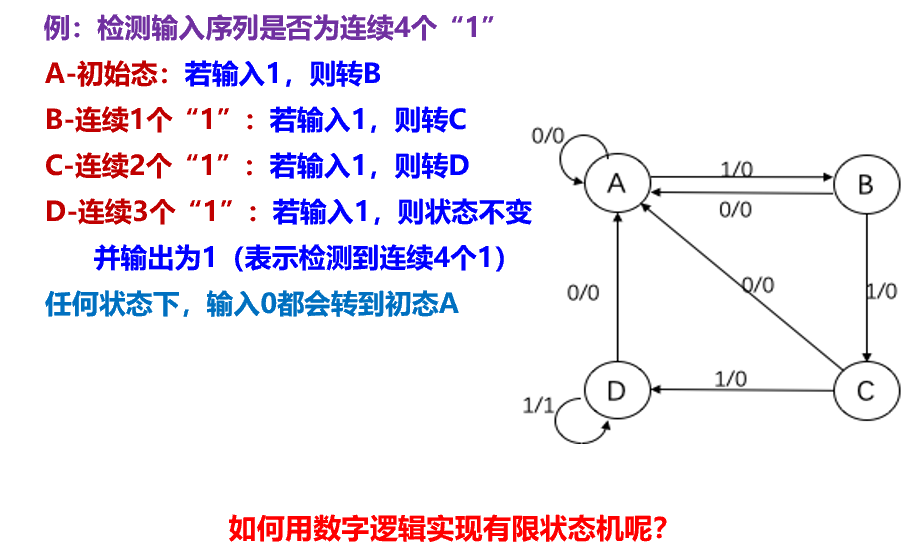

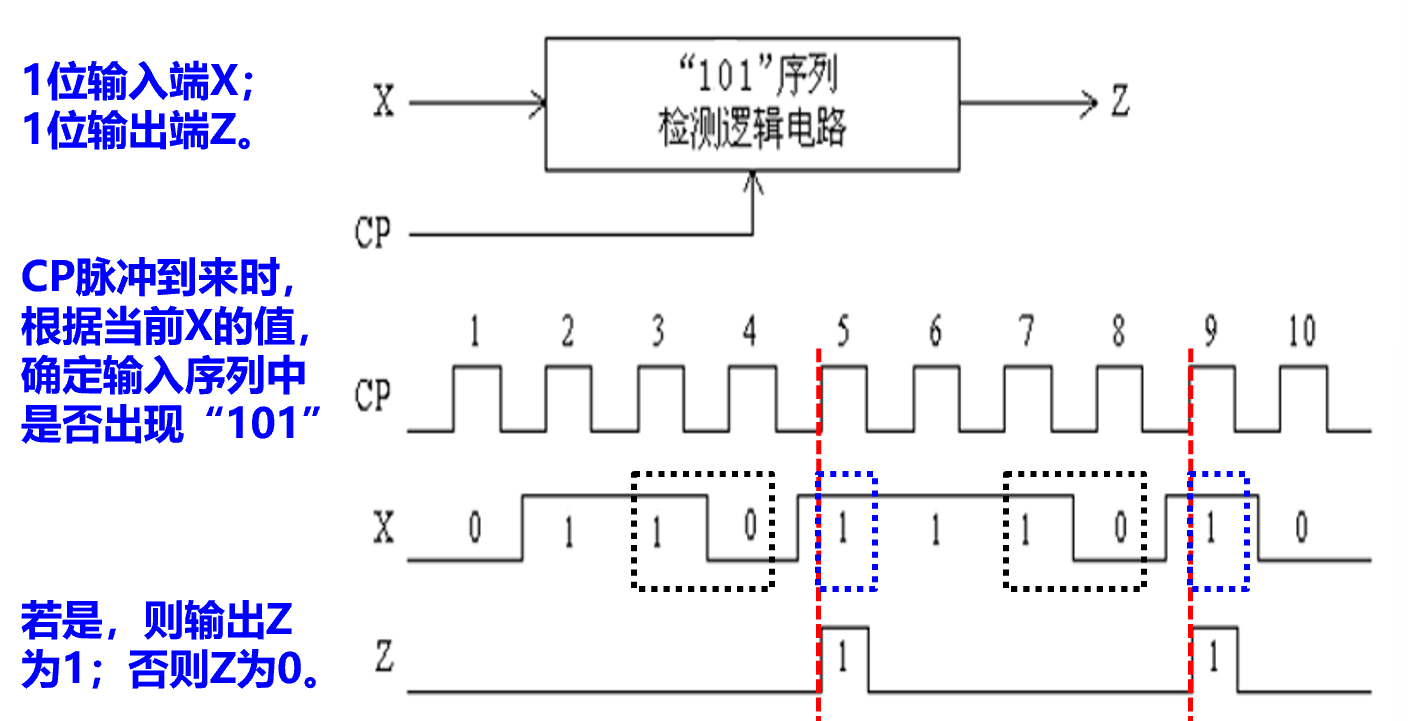

- 以检测一连串0/1输入序列中是否出现“101”为例

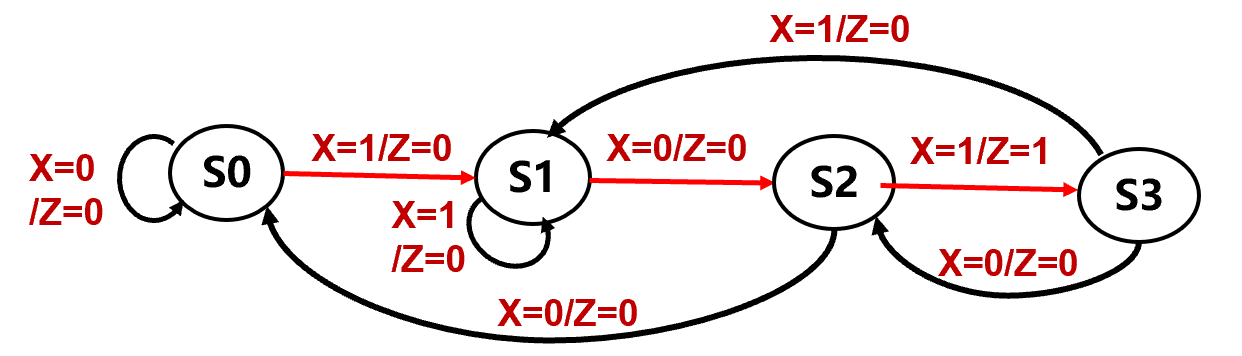

状态图/状态表设计¶

- 设定任一状态为电路的初始状态,从初始状态开始,分析每一个状态在不同输入作用下的状态转移和输出取值

- 如果某状态下出现的输出响应(次态、输出)不能用已有状态表示,则产生新的状态;

- 重复直到不产生新状态为止。

- 常用Z表示输出

- 状态图

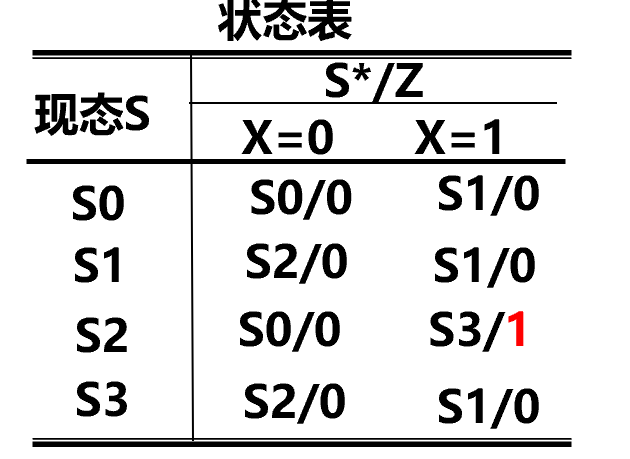

- 状态表

- 状态转移的要求

- 互斥性:每个状态触发的所有状态转换路径上的转换条件必须是互斥的

- 完备性:每个状态出发的所有状态转换路径上的转移表达式的逻辑或等于1

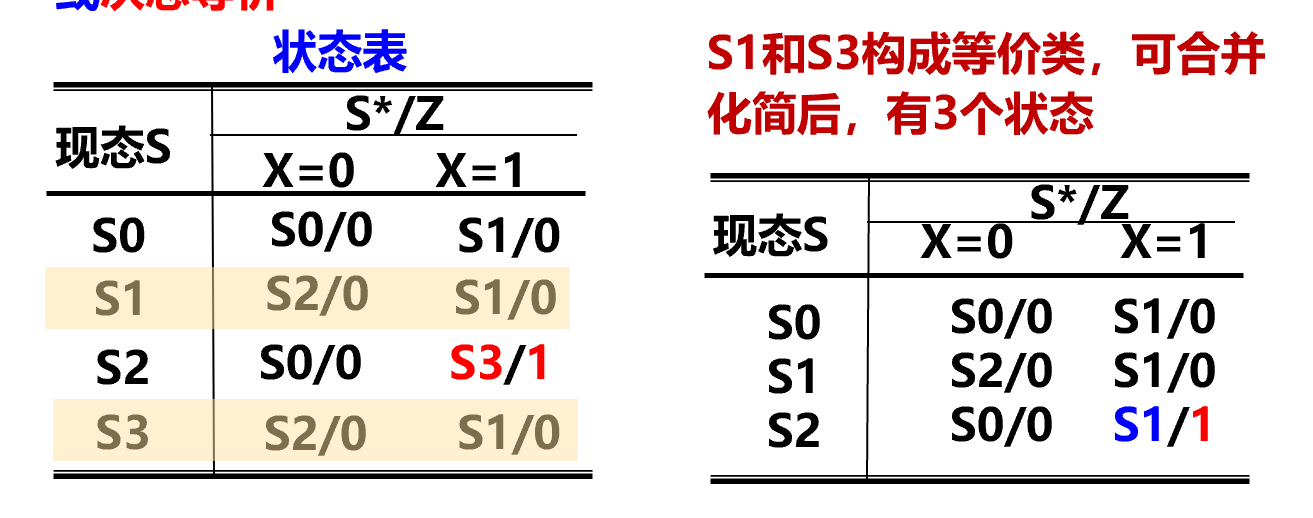

状态化简和状态编码¶

- 合并等价状态(具有相同的输入和等价/相同的次态)

-

-

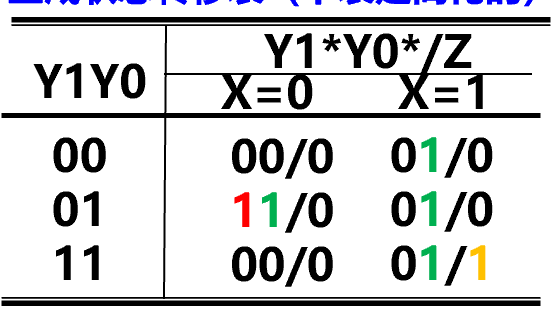

对状态中每一个状态赋予唯一的二进制编码,也称状态赋值,使用相邻法寻找较优编码方案

- 若两个状态的次态相同,则对应编码应尽量相邻(编码相邻的含义是指两个编码的码距为1,即两个编码中只有一位不同)

- 同一个现态的各个次态其编码应尽量相邻

-

若两个现态的输出相同,则他们的编码应尽量相邻

-

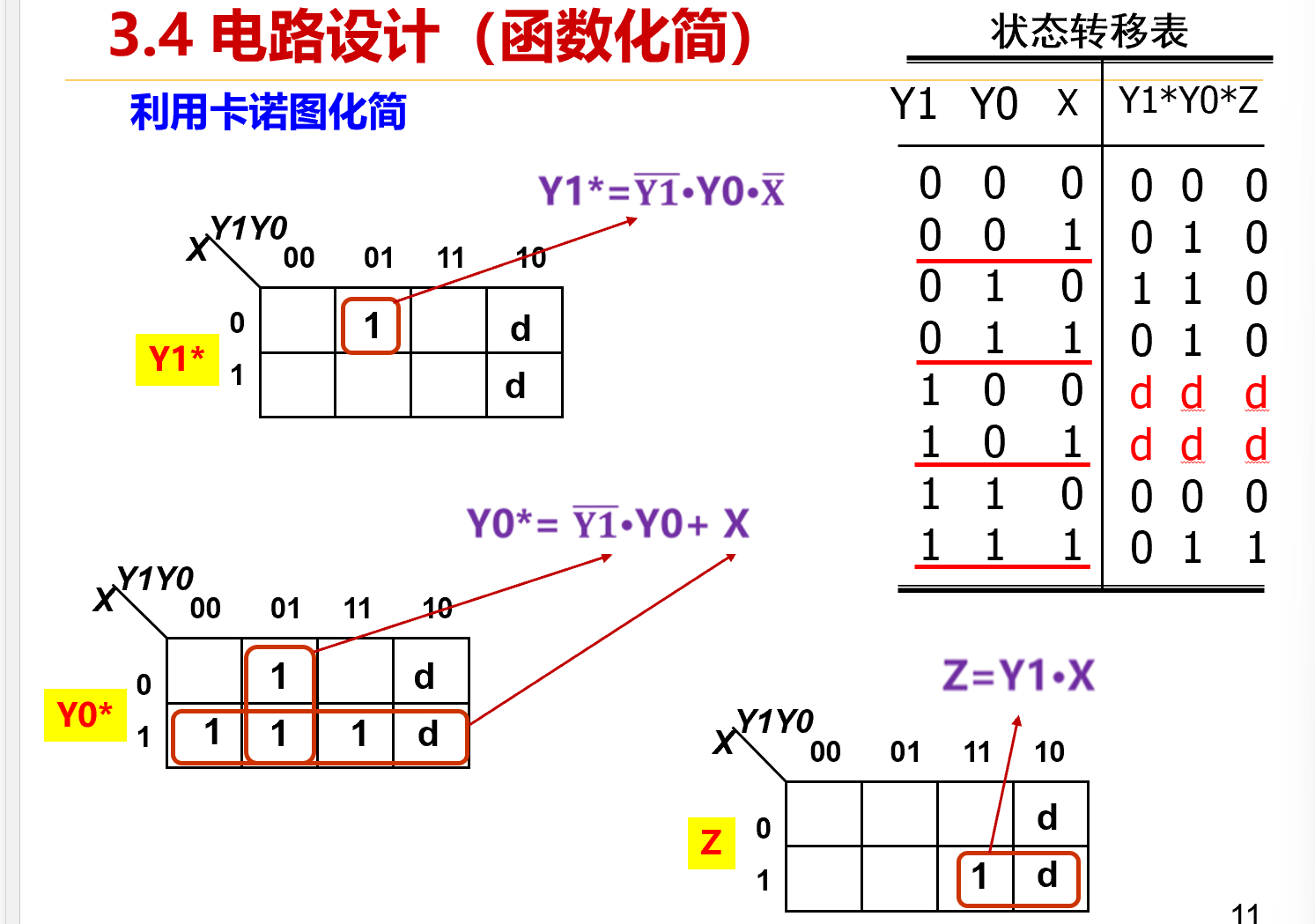

得到转移表

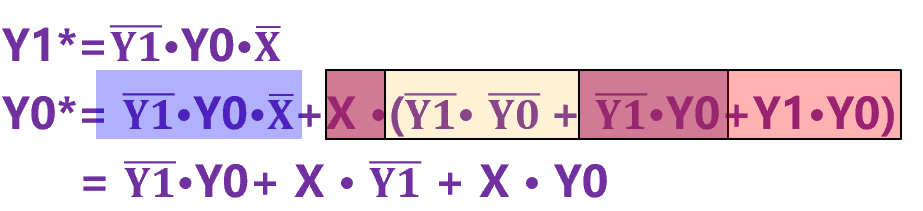

- 得到次态逻辑函数和输出逻辑函数

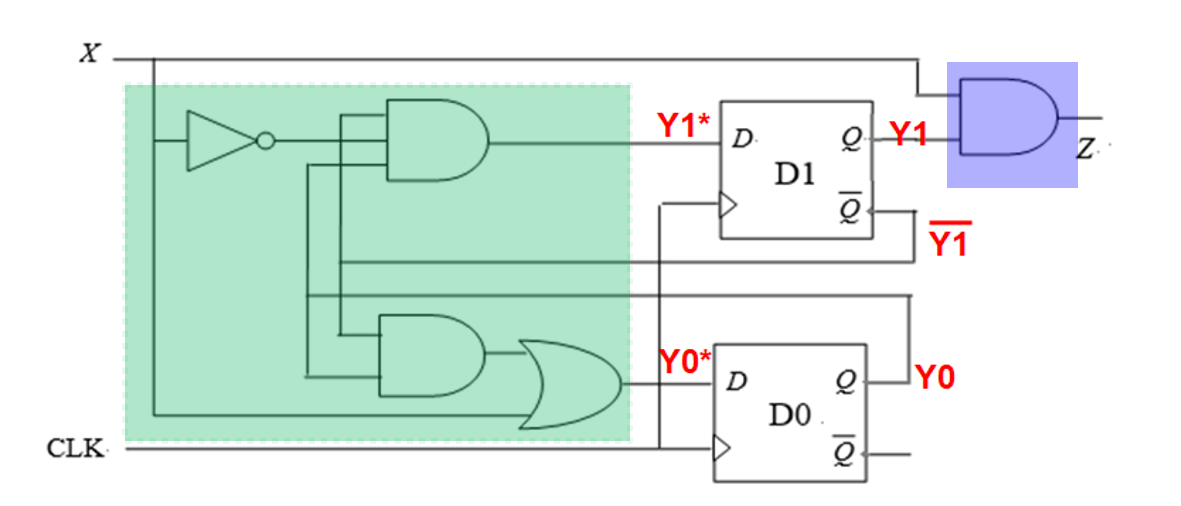

- \(Z=Y_1\cdot Y_0 \cdot X+Y_1 \cdot \overline{Y_0}\cdot X=Y_1\cdot X\)

- 可以使用卡诺图对次态逻辑函数进行化简

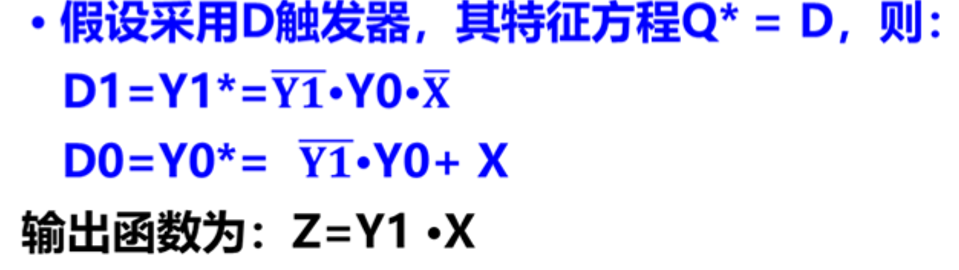

电路设计¶

- 根据选择的次态函数和选择的状态记忆单元,推导出激励函数

- 通过触发器旧状态\(Y_0 \ Y_1\)以及输入\(X\)得到触发器新状态

- 由于状态码为两位,因此需要使用两个 D 触发器

电路设计后的分析¶

未用状态分析¶

- 通常编码空间比状态机的状态集合大,因而存在未用状态

- 若电路加电后进入未用状态,且在未用状态之间形成循环转换而无法进入工作状态,则称其为“挂起”现象,即无法自启动

- 若时序逻辑电路中的触发器具有预置功能,则可以通过预置处理,使电路进入正常的初始工作状态,从而避免“挂起”

-

可利用未用状态的无关项进行化简。但需对未用状态进行分析,以判定电路进入未用状态时能否在有限个时钟周期后进入工作状态。若能,且没有错误输出,则称电路为具有“自启动”能力;若不能或有错误输出,则需调整电路设计

-

利用了状态10作为无关项化简,当处于未用状态10时分析:

- 即存在错误输出,因此需要调整输出模块的设计

-

重新设计输出函数(调整为化简之前的表达式)\(Z=Y_1\cdot Y_0\cdot X\)

-

无法自启动的改进:

- 无法自启动通常是由于使用了无关项化简,应该考虑还原函数,改为不使用无关项进行化简

难点¶

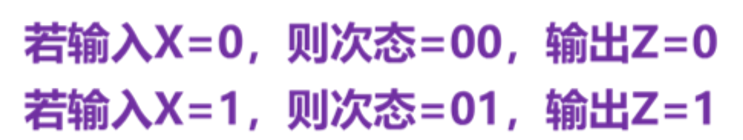

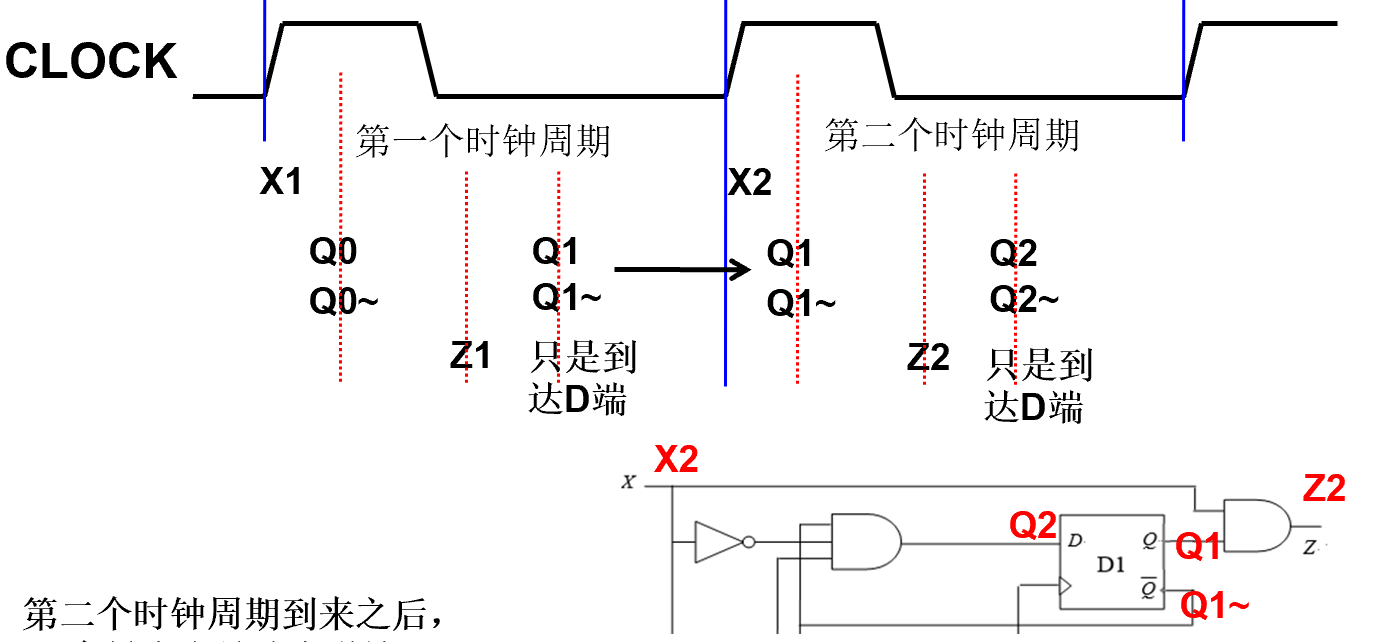

定时分析¶

- 电路的工作频率与组合逻辑电路传输延迟、触发器建立和保持时间、触发器传输延迟等密切相关。

-

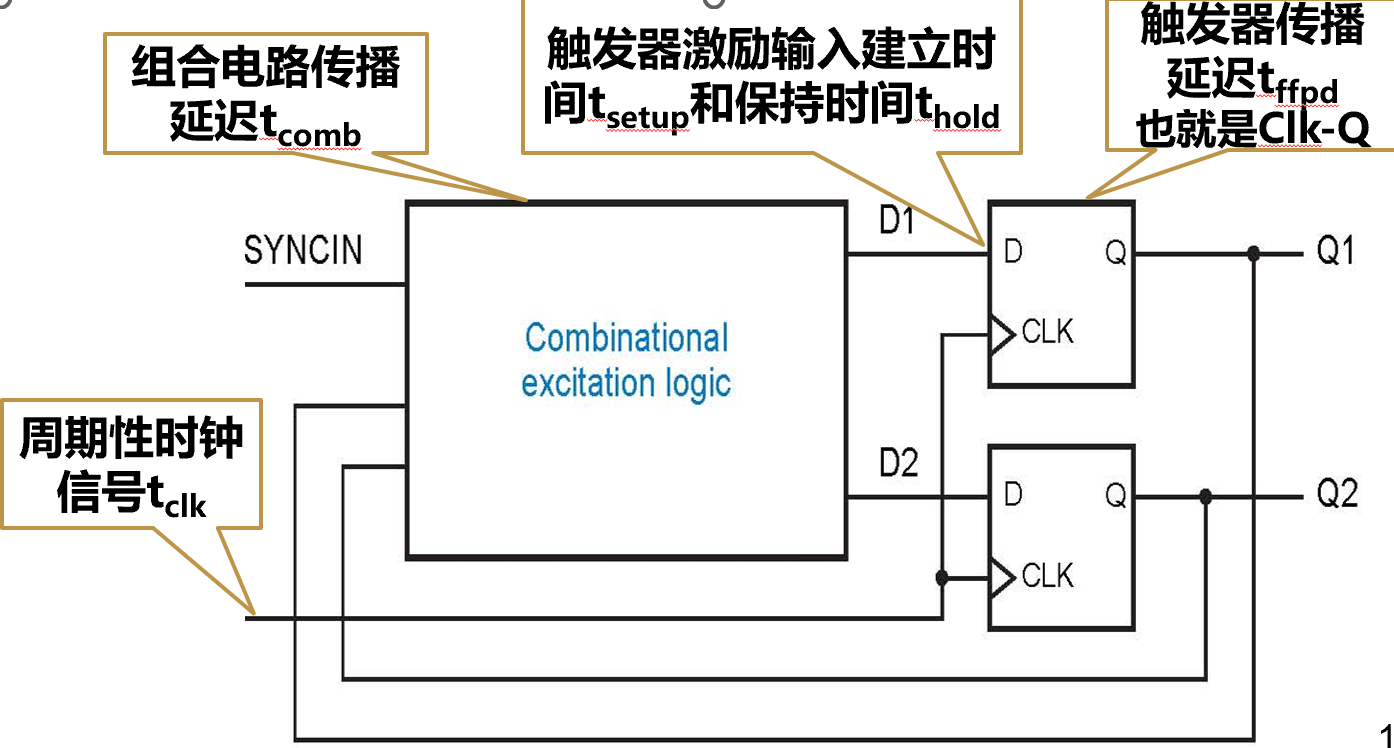

-

- X1 会最先有效稳定送达

- 触发器 Q 端经过 clk-Q 延迟之后,变成初始值 Q0

- 经过次态运算逻辑延迟 (组合逻辑电路延迟) 之后,基于 Q0和 X1计算出 Q1,并达到触发器的 D 端(在第二个时钟周期到来之前,D 端必须保持稳定超过setup 时间)

-

经过输出运算的延迟之后,基于 Q0和 X1完成对 Z1的计算,且该结果不影响其它过程,所以这个延迟只要小于时钟周期就行了,与次态计算无关

-

- 算出的 Q1保持不变,稳定在触发器的 D 端(hold 时间)

- 然后,触发器 Q 端经过 clk-Q 延迟之后,变成 Q1

- 过了次态运算逻辑延迟之后,基于 Q1和 X2,算出了 Q2,并到达触发器 D 端(第3个时钟周期到来之前,这个 D 端必须保持稳定超过 setup 时间)

-

过了输出运算延迟之后,基于 Q1和 X2完成了 Z2的计算

-

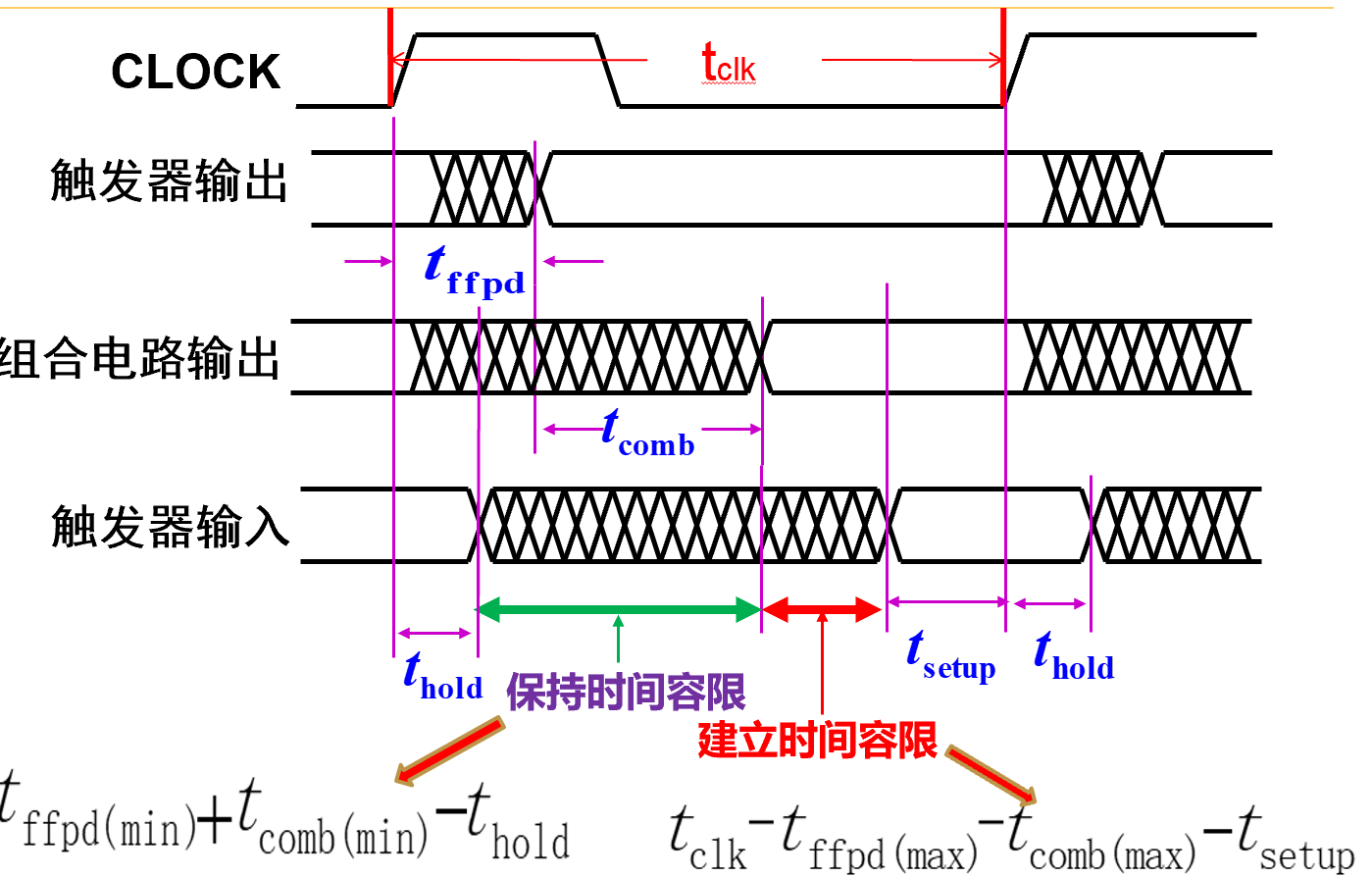

时间容限

- 时间容限指为保证电路正常工作某信号定时所允许的时间范围,都大于 0

- \(t_{ffpd}\) 表示触发器从输入到输出改变的延时

- 建立时间\(t_{clk} - t_{ffpd(max)} - t_{comb(max)} \geq t_{setup}\)

- 保持时间要求:确保数据在时钟沿到来之前然稳定了足够长的时间。

- 即:

- 保持时间容限\(t_{ffpd(min)} + t_{comb(min)} \geq t_{hold}\)

- 设定时间要求:确保数据在时钟沿到来之后稳定了足够长的时间。

时序逻辑部件¶

计数器¶

- 一般从0开始计数,在达到最大计数值时输出一次计数完成信号,并重新开始计数,最大计数值为计数器的模。

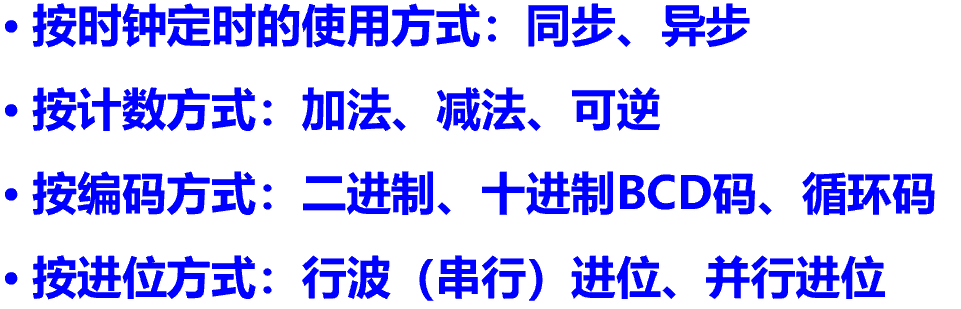

- 分类

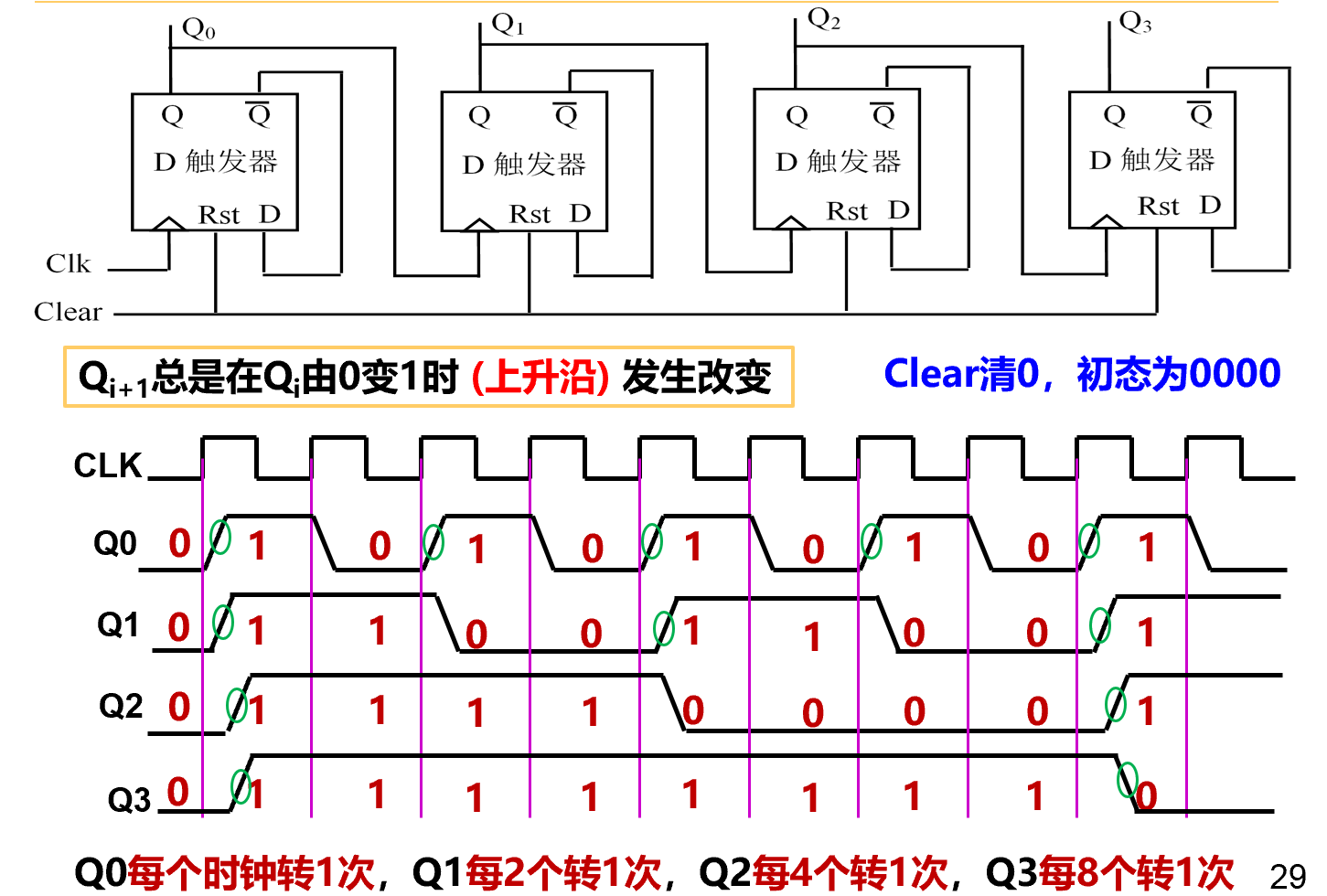

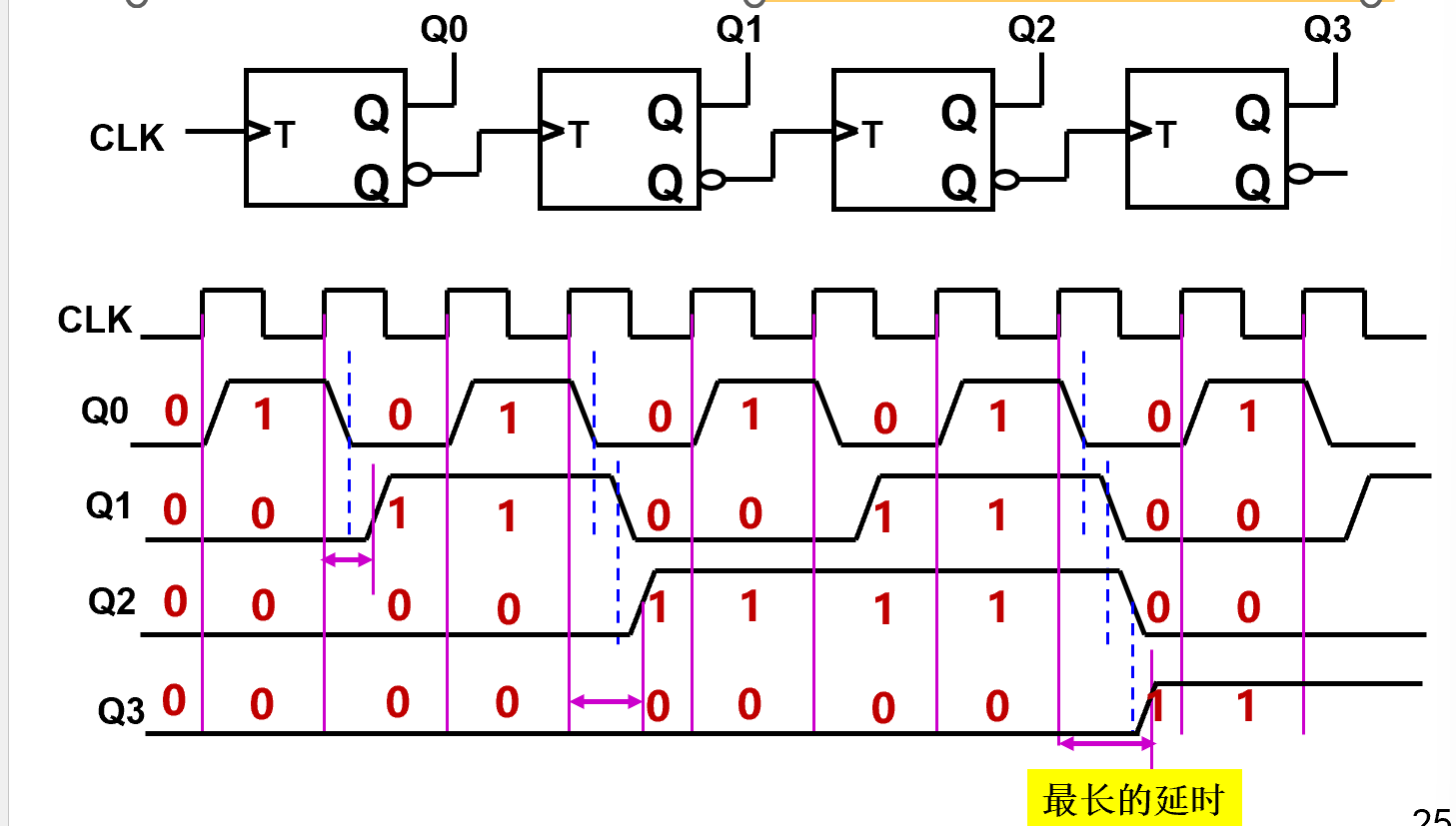

异步行波加法计数器¶

- 用T 触发器实现(上升沿触发),激励输入串行传递,每个时钟周期传递一次。

- \(Q_3Q_2Q_1Q_0\)转换过程为:\(0000->0001->0010->\dots->1111\)

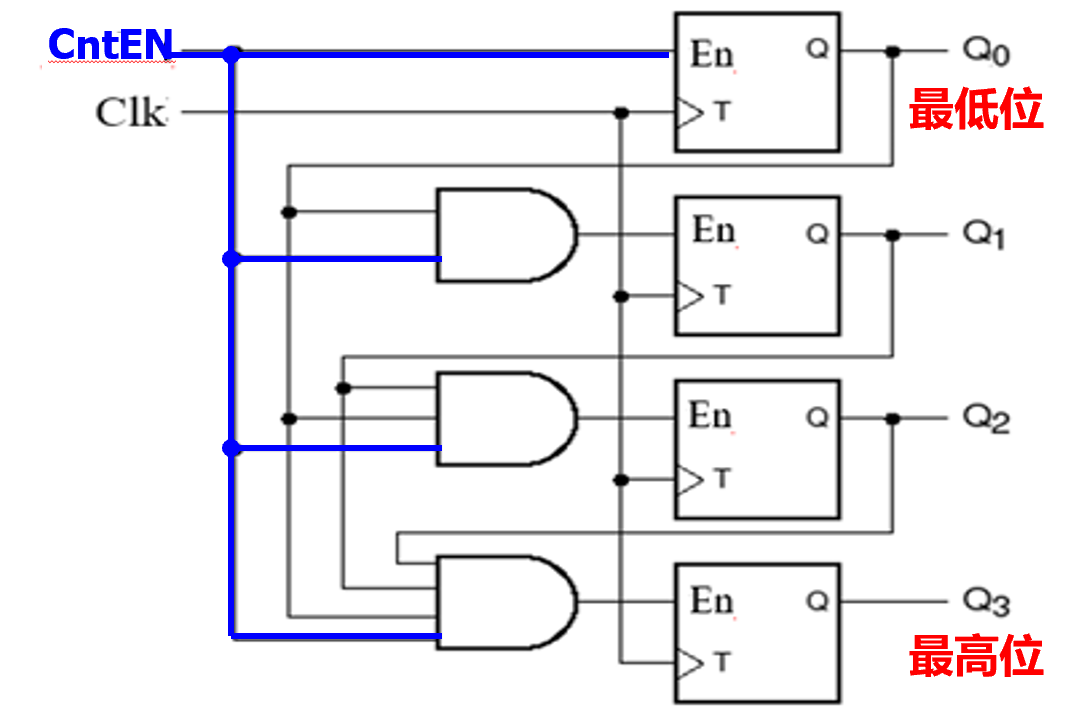

同步并行加法计数器¶

- 所有触发器共用同一个时钟信号,在时钟信号边沿到达后,所有触发器的输出同时发生变化。

- 对于 Q1、Q2和 Q3,只有在其所有低位状态都是1的情况下,下个时钟边沿到来后才会发生状态反转。(即发生了进位的情况)

二进制异步行波减法计数器¶

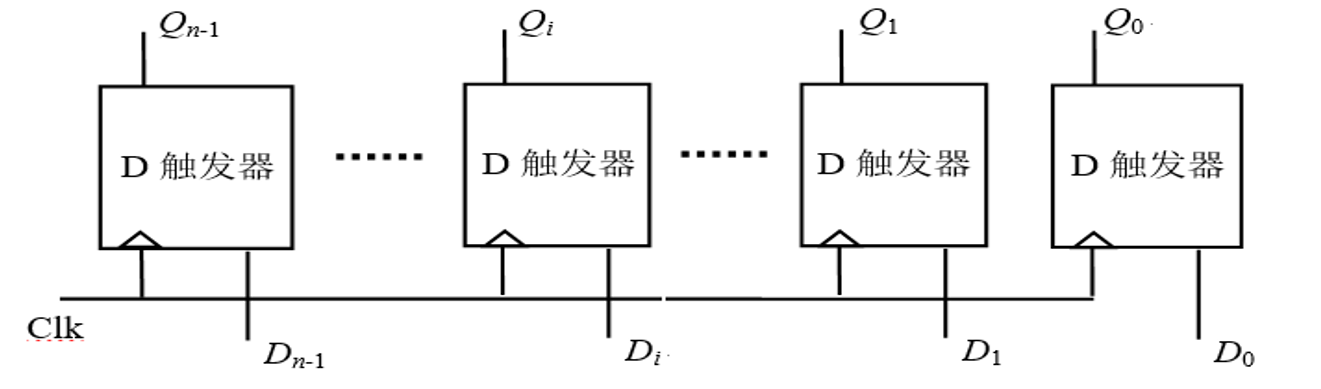

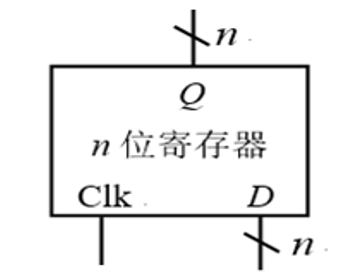

寄存器¶

- 用来暂存信息,可直接由若干个触发器组成

- 寄存器是一种时序逻辑电路,但只包含存储电路 ,在没有新的CLK脉冲来之前,寄存器一定能保存原有内容不变

- 附加一些控制电路就能够实现:置零、保持( CLK信号到达时触发器不随D端的输入信号而改变状态,保持原来的状态不变)等功能。

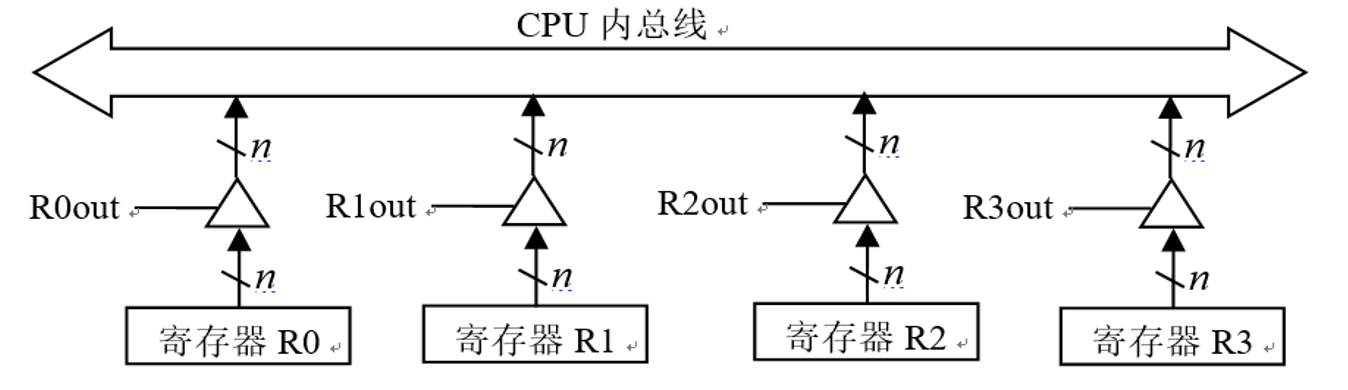

- 寄存器通过三态门和总线互连,任何时刻至多只能一个Rout有效

寄存器堆¶

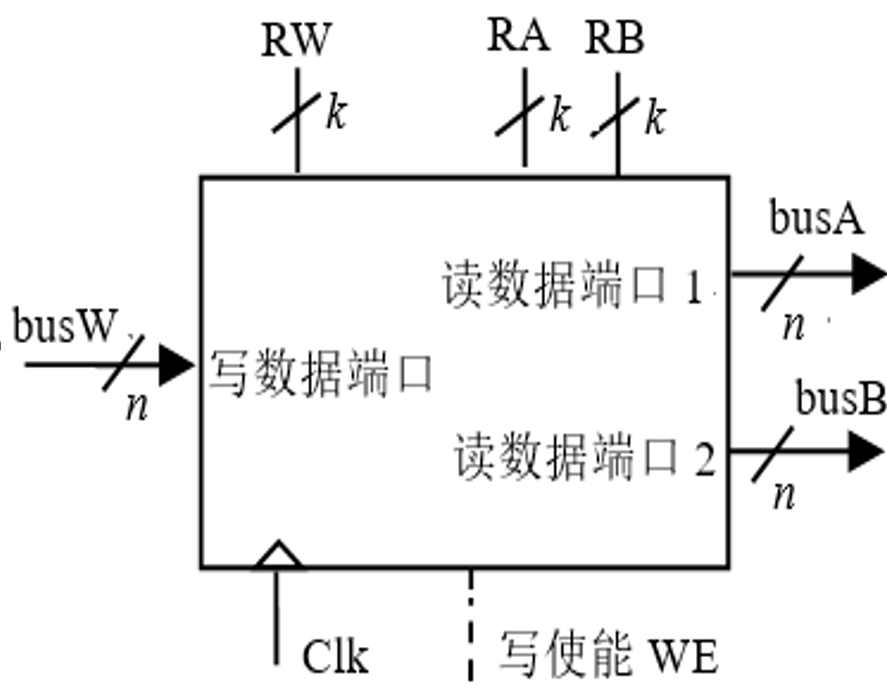

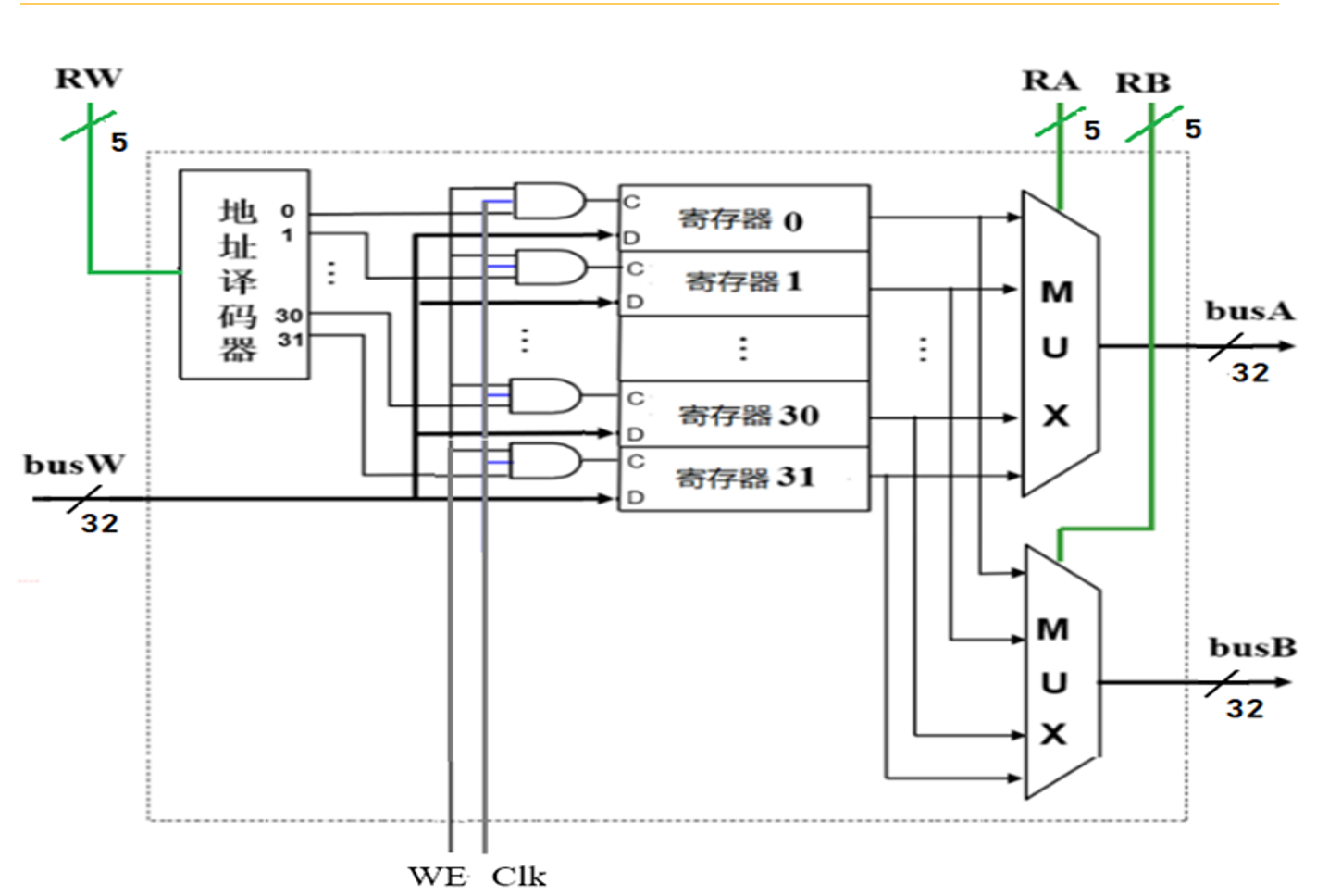

- 寄存器堆:CPU内部用于暂存指令执行过程中的中间数据,也称通用寄存器组GPRs,由许多寄存器组成,每个寄存器有一个编号,CPU可对指定编号的寄存器进行读写。

- 寄存器堆中共有 \(2^k\) 个寄存器,每个寄存器位数为 n

- RA和RB分别是读口1和读口2的寄存器编号,RW是写口的寄存器编号

- 读操作属于组合逻辑操作; 写操作属于时序逻辑操作,需要时钟信号Clk和写使能信号WE的控制

- 写数据时,只要保证时钟信号clk到来前,地址RW和写使能WE信号有效,且busW已经稳定一个setup time以上即可

- 读数据时,由RA、RB分别选择对应寄存器中的内容送busA、busB

移位寄存器¶

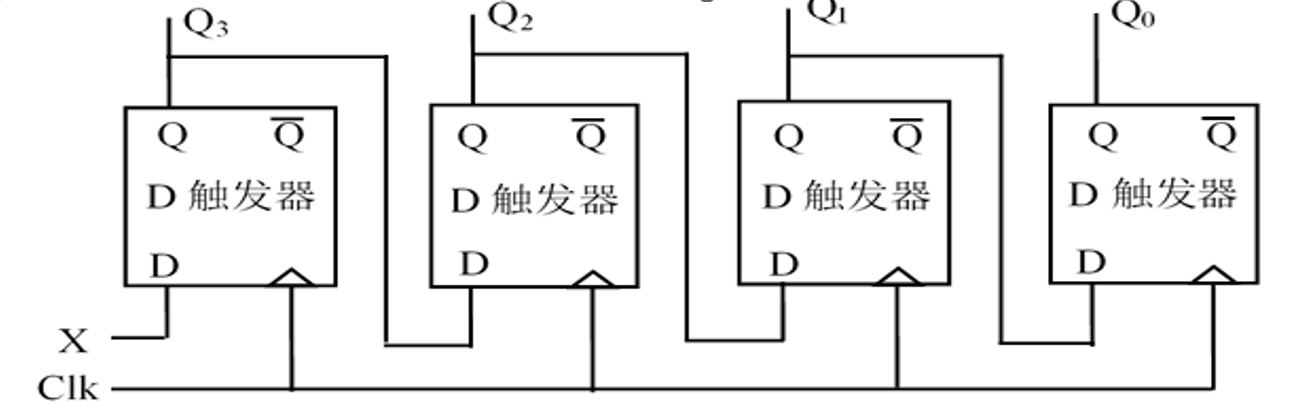

- 能够实现暂存信息的左移或右移功能,通常由时钟信号控制

-

-

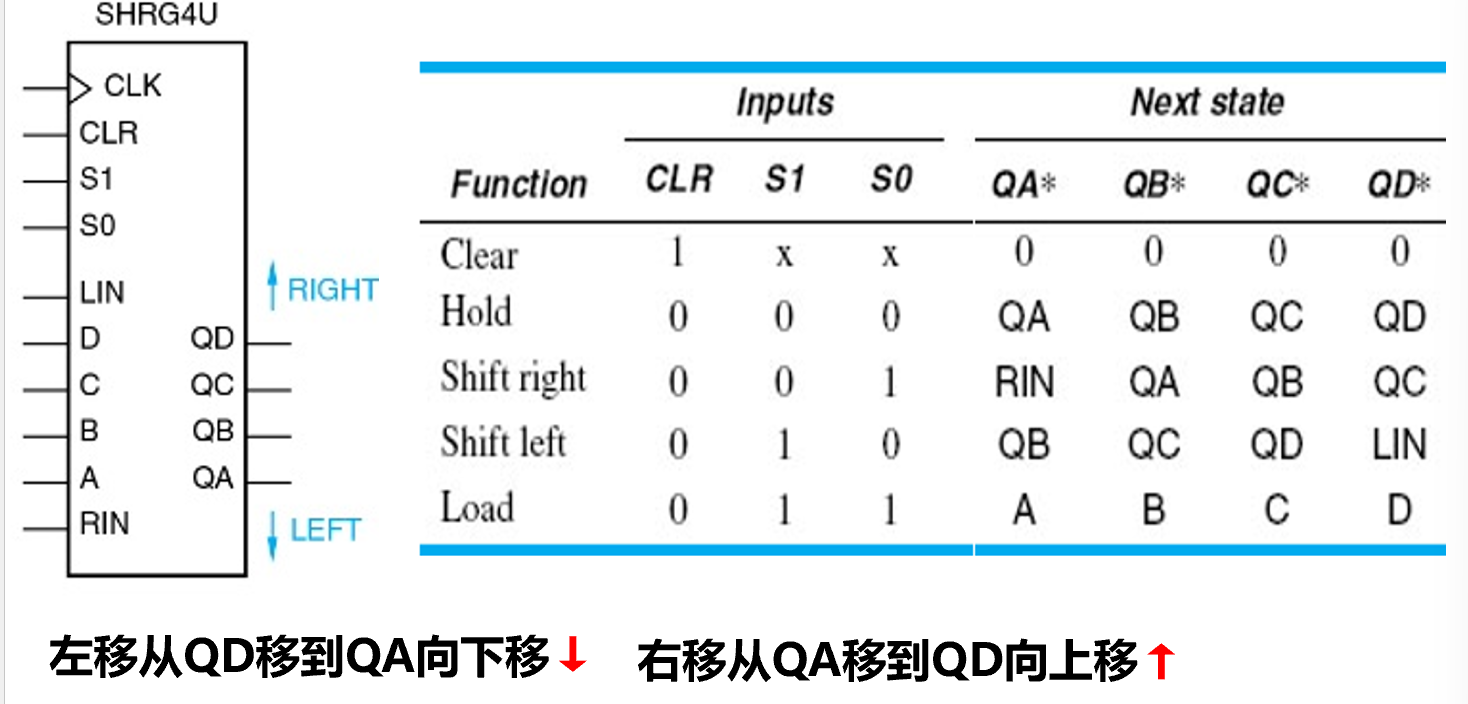

4位通用移位寄存器,如74X194;具有数据左移、数据右移、数据保持和数据载入功能;用CLR,S1,S0这三个信号的排列组合来表示不同功能

桶型移位寄存器¶

- 一次移动多位。组合逻辑电路,采用大量多路选择器实现。只有移位功能 没有寄存功能

- 非循环移位:

- 逻辑右(左)移:高(低)位补0

- 算术右(左)移:高(低)位补符

存储器¶

- 寄存器由触发器构成用来存储少量数据,速度快

- 存储器阵列用来存储大量数据,速度较慢

- 存储器阵列中每位数据对应一个记忆单元,称为存储元

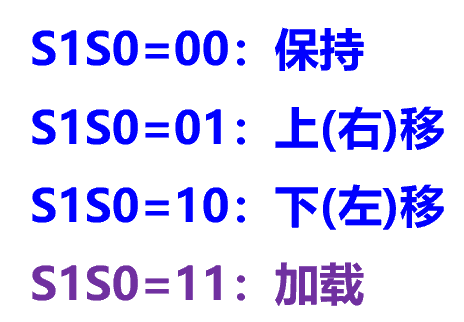

ROM¶

- 只读存储器,非易失性存储器,电源断电数据不会消失

- 如存放 BIOS 自检程序、微程序控制器中的控制存储器

- 根据MOS晶体管的有无来区分存储0/1,不同类型的ROM主要区别在于MOS晶体管的特性不同

- 译码器输出称为字线,高有效

RAM¶

- 随机存取存储器,易失性存储器

- 静态RAM:SRAM

- 动态RAM:DRAM

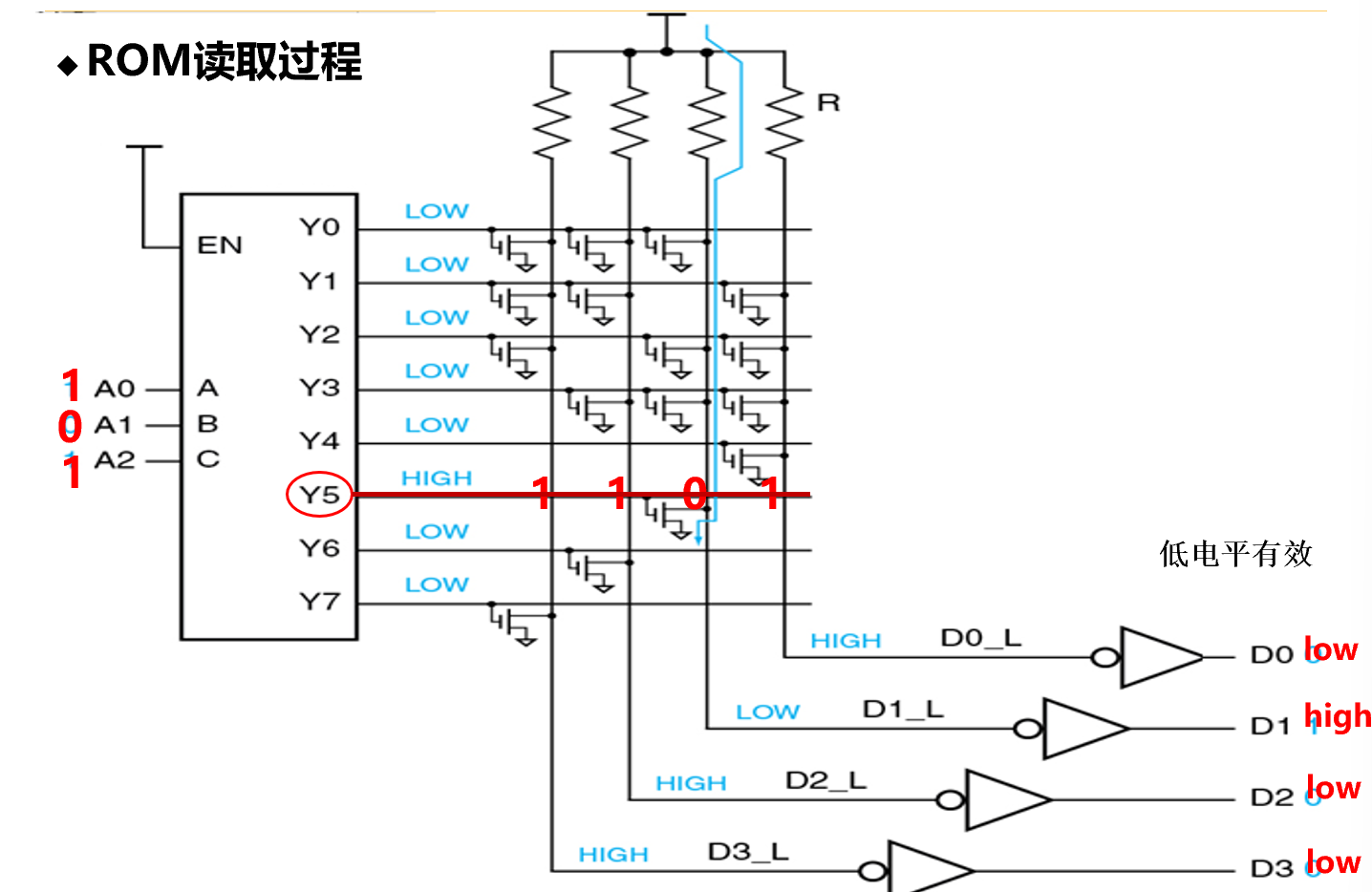

SRAM¶

- 存储单元使用6个MOS晶体管来实现

- 优点:读写速度快、无需刷新。

- 缺点:器件多,因此价格高、功耗大、集成度低。

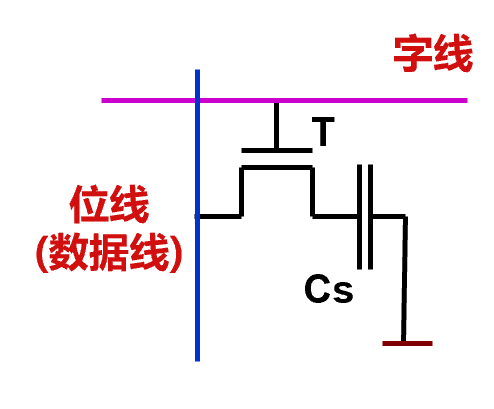

DRAM¶

- 单MOS管,电容上存有大量电荷为1,否则0

- 优点:电路元件少,功耗小,集成度高,用于构建主存储器

- 缺点:速度慢,是破坏性读出(需读后再生),需定时刷新